IMPLEMENTATION OF THE FAST FOURIER TRANSFORM

IMPLEMENTATION OF THE FAST FOURIER TRANSFORM

The Verilog source code for the FFT is included in appendixes. Page 26. 6. THIS PAGE INTENTIONALLY LEFT BLANK. Page 27. 7. II. BACKGROUND AND PRIOR WORK. The

DESIGN AND SIMULATION OF 32-POINT FFT BY RADIX-2

DESIGN AND SIMULATION OF 32-POINT FFT BY RADIX-2

FFT is an algorithm that computes the discrete Fourier transform of a sequence. method of debugging embedded C code is the same as VHDL or Verilog. ModelSim ...

Analysis and implementation of SDF Radix-2 FFT processor using

Analysis and implementation of SDF Radix-2 FFT processor using

And we will use pipeline FFT processor and single path delay feedback pipeline processor for our design.The research is conducted by VERILOG codes running on

The Fast Fourier Transform in Hardware: A Tutorial Based on an

The Fast Fourier Transform in Hardware: A Tutorial Based on an

20-May-2014 Let us take a look at the sequencing of the data addresses and the twiddle factor addresses generated with this code. We have verified the ...

Implementation of Pipelined FFT Processor on FPGA Microchip

Implementation of Pipelined FFT Processor on FPGA Microchip

01-Jun-2017 Fast Fourier transform (FFT) is an efficient algorithm for discrete Fourier ... pipelined FFT processor written in Verilog code. These outputs ( ...

IMPLEMENTATION OF FAST FOURIER TRANSFORM USING

IMPLEMENTATION OF FAST FOURIER TRANSFORM USING

Verilog implementation of floating point FFT with reduced generation logic is the proposed architecture where the two inputs and two outputs of any

Analysis and implementation of SDF Radix-2 FFT processor using

Analysis and implementation of SDF Radix-2 FFT processor using

And we will use pipeline FFT processor and single path delay feedback pipeline processor for our design.The research is conducted by VERILOG codes running on

Implementation of 64-Point FFT Processor Based on Radix-2 Using

Implementation of 64-Point FFT Processor Based on Radix-2 Using

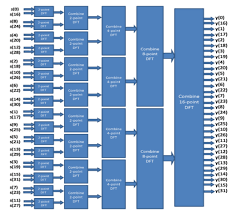

Proposed architecture is implemented using verilog HDL. XILINX ISE 12.1. The performance of the proposed architecture is implemented in terms of relative error.

Universal FFT core generator

Universal FFT core generator

Figure 4.13 provides pseudo-code in Verilog that defines the Kernel module. 4.6.4 ROM Module. The twiddle factors necessary for the one-dimensional DFT

Analysis and implementation of SDF Radix-2 FFT processor using

Analysis and implementation of SDF Radix-2 FFT processor using

And we will use pipeline FFT processor and single path delay feedback pipeline processor for our design.The research is conducted by VERILOG codes running

Verilog Implementation of Floating Point FFT With Reduced

Verilog Implementation of Floating Point FFT With Reduced

The FFT requires only a few lines of code; it is one of the mainly intricate methods in DSP. J.W. Cooley and J.W. Tukey are given recognition for.

Design and Implementation of 8 point FFT using Verilog HDL

Design and Implementation of 8 point FFT using Verilog HDL

This 8 point FFT design is implemented using Verilog HDL in Xilinx ISE Software. General Terms. Discrete Fourier Transform Fast Fourier Transform

IMPLEMENTATION OF FAST FOURIER TRANSFORM USING

IMPLEMENTATION OF FAST FOURIER TRANSFORM USING

Verilog implementation of floating point FFT with reduced generation logic is the proposed lines of code; it is one of the mainly intricate methods.

Appendix A. Verilog Code of Design Examples

Appendix A. Verilog Code of Design Examples

The next pages contain the Verilog 1364-2001 code of all design examples. The old style Verilog 1364-1995 output reg fft_valid // FFT output is valid.

The Fast Fourier Transform in Hardware: A Tutorial Based on an

The Fast Fourier Transform in Hardware: A Tutorial Based on an

Ordibehesht 30 1393 AP The arrays Twr and Twi contain the lookup table of twiddle factors. Since this code is run on a personal computer

Implementation of Fast Fourier Transform in Verilog

Implementation of Fast Fourier Transform in Verilog

The use of FFT is very efficient and vast in the field of Digital signal Processing and Communication. The. Discrete Fourier Transform(DFT)can be implemented

Implementation of 64-Point FFT Processor Based on Radix-2 Using

Implementation of 64-Point FFT Processor Based on Radix-2 Using

A Fast Fourier transform is an efficient algorithm to compute Proposed architecture is implemented using verilog HDL ... Algorithm in section II is.

Implementation of Pipelined FFT Processor on FPGA Microchip

Implementation of Pipelined FFT Processor on FPGA Microchip

Khordad 11 1396 AP FFT processor is a hardware implementation for FFT algorithm. ... pipelined FFT processor written in Verilog code. These outputs (DOR and.

Volume 177 No. 11, October 2019

4 Design and Implementation of 8 point FFT using Verilog HDLSonali Kangralkar

Student

VLSI Design & Embedded System

KLE Dr.M.S.Sheshgiri College of Engineering &

Technology

Rajashri Khanai, PhD

Professor

Department of Electronics and Communication

KLE Dr.M.S.Sheshgiri College of Engineering &

Technology

ABSTRACT

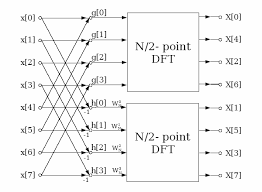

The importance of Digital Signal Processing (DSP) algorithms have increased drastically in recent times, the two important techniques of DSP are the Discrete Fourier Transform(DFT) and the Fast Fourier Transform(FFT). DFT is broadly used in the applications such as convolution, linear filtering etc. Another algorithm to compute DFT efficiently is the Fast Fourier Transform (FFT). Fast Fourier Transform processor has an important role in the field of communication system such as audio broadcasting and digital video etc. This paper deals with the designing of an 8 point FFT using radix-2 DIT FFT algorithm. This 8 point FFT design is implemented using Verilog HDL in Xilinx ISE Software.General Terms

Discrete Fourier Transform, Fast Fourier Transform, Decimation in Time, Decimation in Frequency, algorithmKeywords

Digital Signal Processing (DSP), Discrete Fourier Transform (DFT), Fast Fourier Transform (FFT), Split-Radix FFT (SRFFT), Decimation in Time FFT(DIT-FFT), Decimation inFrequency(DIF-FFT)

1. INTRODUCTION

Digital signal processing is one of the frequently used techniques for video and audio applications. Many techniques are available in the DSP domain to analyze the video or audio signals. Discrete Fourier Transform (DFT) is widely used algorithm in digital signal processing applications such as linear filtering, convolution, spectrum analysis and correlation. DFT is said to be a frequency domain representation of original Sequence.X (k) = σT:J;Aିquotesdbs_dbs11.pdfusesText_17

[PDF] fft codechef

[PDF] fft complex number

[PDF] fft complex number frequency

[PDF] fft complex number input

[PDF] fft complex number meaning

[PDF] fft complex number result

[PDF] fft convolution complexity

[PDF] fft eigenvalues

[PDF] fft example arduino

[PDF] fft example by hand

[PDF] fft example c

[PDF] fft example data

[PDF] fft example in r

[PDF] fft example problem

Implementation of Fast Fourier Transform (FFT) on FPGA using

Implementation of Fast Fourier Transform (FFT) on FPGA using