ECS 50 8086 Instruction Set Opcodes Operation Operands Opcode

ECS 50 8086 Instruction Set Opcodes Operation Operands Opcode

8086 Instruction Set Opcodes. Operation Operands. Opcode. ADC see ADD. ADD opcode + $10 and xx010xxx (ModR/M byte) for $80-$83. ADD r/m8

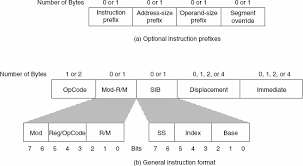

80x86 Instruction Encoding 8086 Instructions Encoding of 8086

80x86 Instruction Encoding 8086 Instructions Encoding of 8086

The first two bytes are called the opcode byte and the addressing mode byte. • The opcode byte specifies the operation the size of.

Intel® 64 and IA-32 Architectures Software Developers Manual

Intel® 64 and IA-32 Architectures Software Developers Manual

Table B-29. Formats and Encodings of SSE3 Floating-Point Instructions ... Opcode/. Instruction. Op/. En. 64/32-bit. Mode. CPUID. Feature. Flag. Description. 66 0F ...

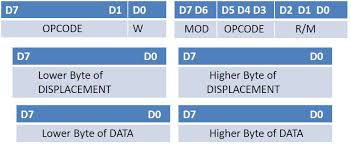

8086(Machine Language Instruction Formats)

8086(Machine Language Instruction Formats)

This format is only one byte long and may have the implied data or register operands. •The least significant 3-bits of the opcode are used for specifying the

8086 Instruction Encoding-1 Encoding of 8086 Instructions ! 8086

8086 Instruction Encoding-1 Encoding of 8086 Instructions ! 8086

Two register instruction; use REG table ! REG w=0 w=1. REG w=0 w=1. 000 AL. AX 8086 Instruction Encoding-12. Examples (Cont'd) ! MOV instruction has seven ...

Intel® 64 and IA-32 Architectures Software Developers Manual

Intel® 64 and IA-32 Architectures Software Developers Manual

Table 2-18 through Table 2-27 certain subsets of AVX instructions may be ... Opcode/. Instruction. Op/. En. 64/32-bit. Mode. CPUID. Feature. Flag. Description.

Intel® 64 and IA-32 Architectures Software Developers Manual

Intel® 64 and IA-32 Architectures Software Developers Manual

Manual. Volume 2A: Instruction Set Reference A-L. NOTE: The Intel® 64 and IA ... Table 2-35 below

MCS·86 ASSEMBLY LANGUAGE CONVERTER OPERATING

MCS·86 ASSEMBLY LANGUAGE CONVERTER OPERATING

• Table C-2 shows the mapping of 8080 directives which convert to 8086 pseudo-directives. Entries in Table C-2 are neither supported by the MCS-86. Assembler

8086 assembler tutorial for beginners (part 1) what is assembly

8086 assembler tutorial for beginners (part 1) what is assembly

Where is a numeric Table of Opcodes? Answer: A list of all 8086 CPU compatible instructions is published here (without numeric opcodes). Only those

The 8086 Microprocessor

The 8086 Microprocessor

Microprocessor 8086 starts operation by fetching. 1 (or 2) byte(s) of instruction code(s) if CS : IP address is odd (even). The 1st byte is always an opcode

ECS 50 8086 Instruction Set Opcodes Operation Operands Opcode

ECS 50 8086 Instruction Set Opcodes Operation Operands Opcode

8086 Instruction Set Opcodes. Operation Operands. Opcode. ADC see ADD. ADD opcode + $10 and xx010xxx (ModR/M byte) for $80-$83.

Week 3 8086/8088 Addressing Modes Instruction Set & Machine

Week 3 8086/8088 Addressing Modes Instruction Set & Machine

searching through a large table of data for a special string of characters Converting Assembly Language. Instructions to Machine Code. OPCODE.

x86 Opcode Structure and Instruction Overview

x86 Opcode Structure and Instruction Overview

x86 Opcode Structure and Instruction Overview v1.0 – 30.08.2011 Opcode table presentation inspired by work of Ange Albertini. MMX SSE{2

8086 Programming

8086 Programming

Oct 23 2012 opcode – same as last example: 111111 000 w = 0. 8-bit destination (memory) operand r/m = 100. (from table) mod could be 01 or 10 depends on ...

Instruction set of 8086 Microprocessor

Instruction set of 8086 Microprocessor

A program written in machine language is referred to as machine code. ADD AX BX. (Opcode) (Destination operand) (Source operand ). Software

Intel® 64 and IA-32 Architectures Software Developers Manual

Intel® 64 and IA-32 Architectures Software Developers Manual

Table 2-23. Type 6 Class Exception Conditions. Exception. Re a l. Virtual-8086. P ro tected and. Comp atib ility. 64-bit. Cause of Exception. Invalid Opcode

Lecture 2 The CPU Instruction Fetch & Execute

Lecture 2 The CPU Instruction Fetch & Execute

IR (opcode) The most significant bits of the instruction make up the opcode. with the the Intel 8086 (from 1979) having n = 20 address lines to current ...

29 Section 29. Instruction Set

29 Section 29. Instruction Set

Table 29-2 gives the opcode field descriptions. For byte-oriented instructions 'f' represents a file register designator and 'd' represents a des-.

Intel Assembler CodeTable 80x86 - Overview of instructions

Intel Assembler CodeTable 80x86 - Overview of instructions

TRANSFER. Flags. Name. Comment. Code. Operation. O D I T S Z A P C. MOV. Move (copy). MOV DestSource Dest:=Source. XCHG. Exchange. XCHG Op1

x86 Instruction Encoding

x86 Instruction Encoding

8086: 1978 16-bit CPU with 16-bit external data bus Opcode