2. Demi Additionneur

2. Demi Additionneur

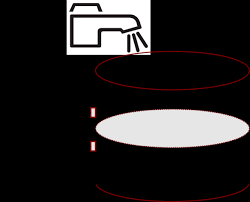

L'addition sur un bit peut se faire par un additionneur complet sur 1 bits. r1 s1 r2 s2 r3 s3 r4 s4 b1 b2 b3.

Architecture des ordinateurs Corrigé du TD 4 : Circuits combinatoires

Architecture des ordinateurs Corrigé du TD 4 : Circuits combinatoires

Rappeler les principes d'un demi-additionneur puis d'un additionneur complet. Déduire de ces principes un circuit logique qui implémente le complément à 2 sur n

Aucun titre de diapositive

Aucun titre de diapositive

La table de vérité de demi-additionneur peut être considérée comme une mémoire de taille 4 fois 2 bits. Les valeurs de la mémoire ont été calculées et.

Les circuits combinatoires

Les circuits combinatoires

2. Demi Additionneur. ○ Le demi additionneur est un circuit combinatoire qui permet de réaliser la somme arithmétique de deux nombres A et B sur un bit

Exercice 1 (Cours-7 points). 1. (2 points) Définir le principe dun

Exercice 1 (Cours-7 points). 1. (2 points) Définir le principe dun

1 juin 2022 3. (3 points) Représenter un circuit logique qui implémente le complément à 2 sur 4 bits à l'aide de demi-additionneurs.

Arithmétique des “computers”

Arithmétique des “computers”

L'UAL (2). Page 5. Demi-Additionneur. ♢ Le demi additionneur est un circuit combinatoire qui permet de réaliser la somme arithmétique de deux nombres A et B

Les systèmes combinatoires

Les systèmes combinatoires

2. Additionneurs: III.2.1. Demi-additionneur: Il s'agit d'additionner deux nombres A et B à 1 seul bit. Il présente deux sorties: S (somme) et. R (retenue)

Note obtenue : 17/20

Note obtenue : 17/20

(demi additionneur et additionneur complet) alors que le système à retenue anticipée utilise 3 On obtient le circuit suivant grâce à 2 demi- additionneurs 2 ...

Ce document est une petite introduction à la modélisation en Sy

Ce document est une petite introduction à la modélisation en Sy

26 sept. 2004 Figure 2-1 : Un module avec ses ports

TP2 Additionneurs S3 AE 1. Demi-additionneur Un demi

TP2 Additionneurs S3 AE 1. Demi-additionneur Un demi

2. Additionneur. En utilisant au moins deux demi-additionneurs de la question 1 construire un additionneur à trois entrée A B C in et sortie S Cout. Il

2. Demi Additionneur

2. Demi Additionneur

L'addition sur un bit peut se faire par un additionneur complet sur 1 bits. r1 s1 r2 s2 r3 s3 r4 s4 b1 b2 b3.

circuits combinatoires suite Ch2

circuits combinatoires suite Ch2

2. Demi Additionneur. ? Le demi additionneur est un circuit combinatoire qui permet de réaliser la somme arithmétique de deux nombres A et B sur un bit.

chapitre-3-les-systemes-combinatoires.pdf

chapitre-3-les-systemes-combinatoires.pdf

2. Additionneurs: III.2.1. Demi-additionneur: Il s'agit d'additionner deux nombres A et B à 1

Chapitre 3 Les circuits combinatoires

Chapitre 3 Les circuits combinatoires

2. Figure 3.2 : Logigramme d'un demi-additionneur. 2.2 Additionneur complet. L'additionneur complet prend deux bits d'entrée et une retenue d'entrée et

Les portes logiques

Les portes logiques

Le demi additionneur effectue la somme de deux bits. S est la somme et R le report. (carry). Ce schéma ne convient cependant que pour additionner 2 nombres de 1

Architecture des ordinateurs Corrigé du TD 4 : Circuits combinatoires

Architecture des ordinateurs Corrigé du TD 4 : Circuits combinatoires

circuit logique qui implémente le complément à 2 sur n bits. Correction : Le demi-additionneur possède deux entrées (x et y) et deux sorties (R et S).

Module EN 201 (les circuits FPGA) TD n°4 – synthèse d

Module EN 201 (les circuits FPGA) TD n°4 – synthèse d

TD n°4 – synthèse d'additionneur dans un circuit FPGA Le demi-additionneur binaire est un circuit qui prend en entrée 2 nombres de 1 bit (A.

Conception de circuits combinatoires Les différentes approches

Conception de circuits combinatoires Les différentes approches

Un circuit intégré est une superposition de couches semi-conductrices

TP n°2 : Etude des circuits combinatoires (II)

TP n°2 : Etude des circuits combinatoires (II)

Le demi-additionneur (semi-adder ou half-adder) est le circuit combinatoire qui réalise l'addition de deux bits sans tenir compte d'une éventuelle retenue

Introduction aux circuits logiques de base

Introduction aux circuits logiques de base

entre eux un demi-additionneur et n-1 additionneurs 1 bit complets. • Le chaînage s'effectue par le biais des retenues propagées a. 3 b. 3 r. 3 s. 3 a. 2.