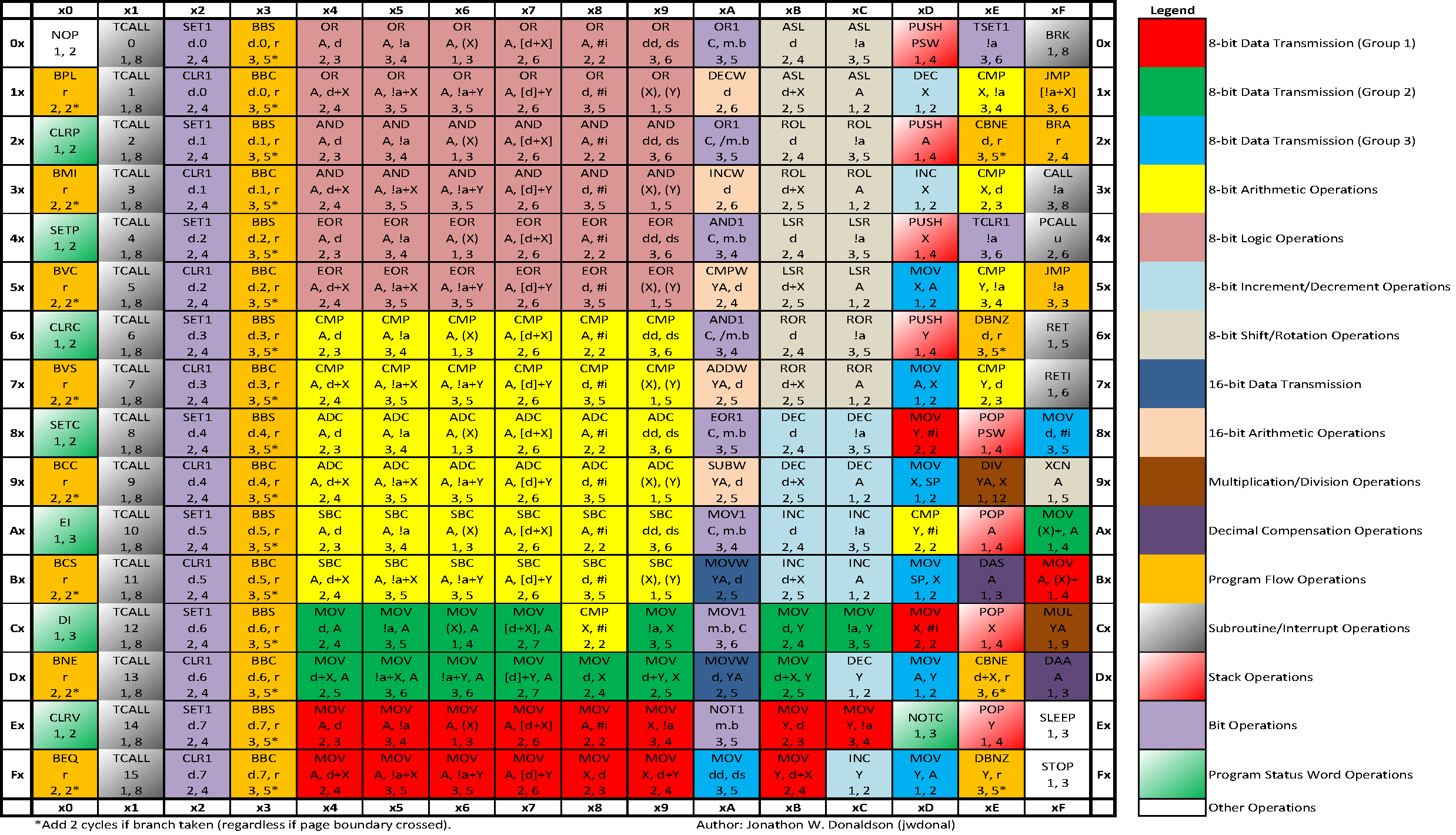

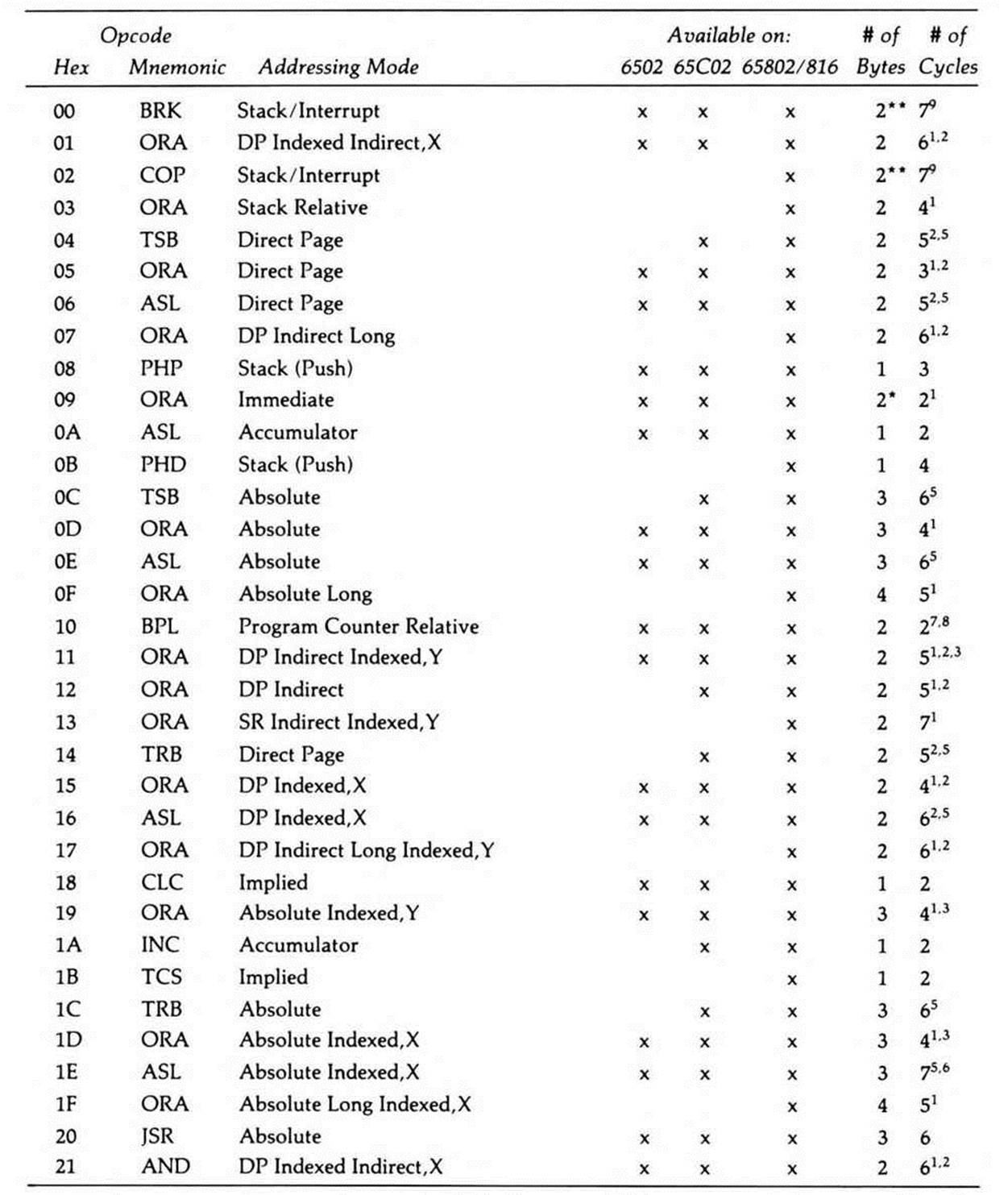

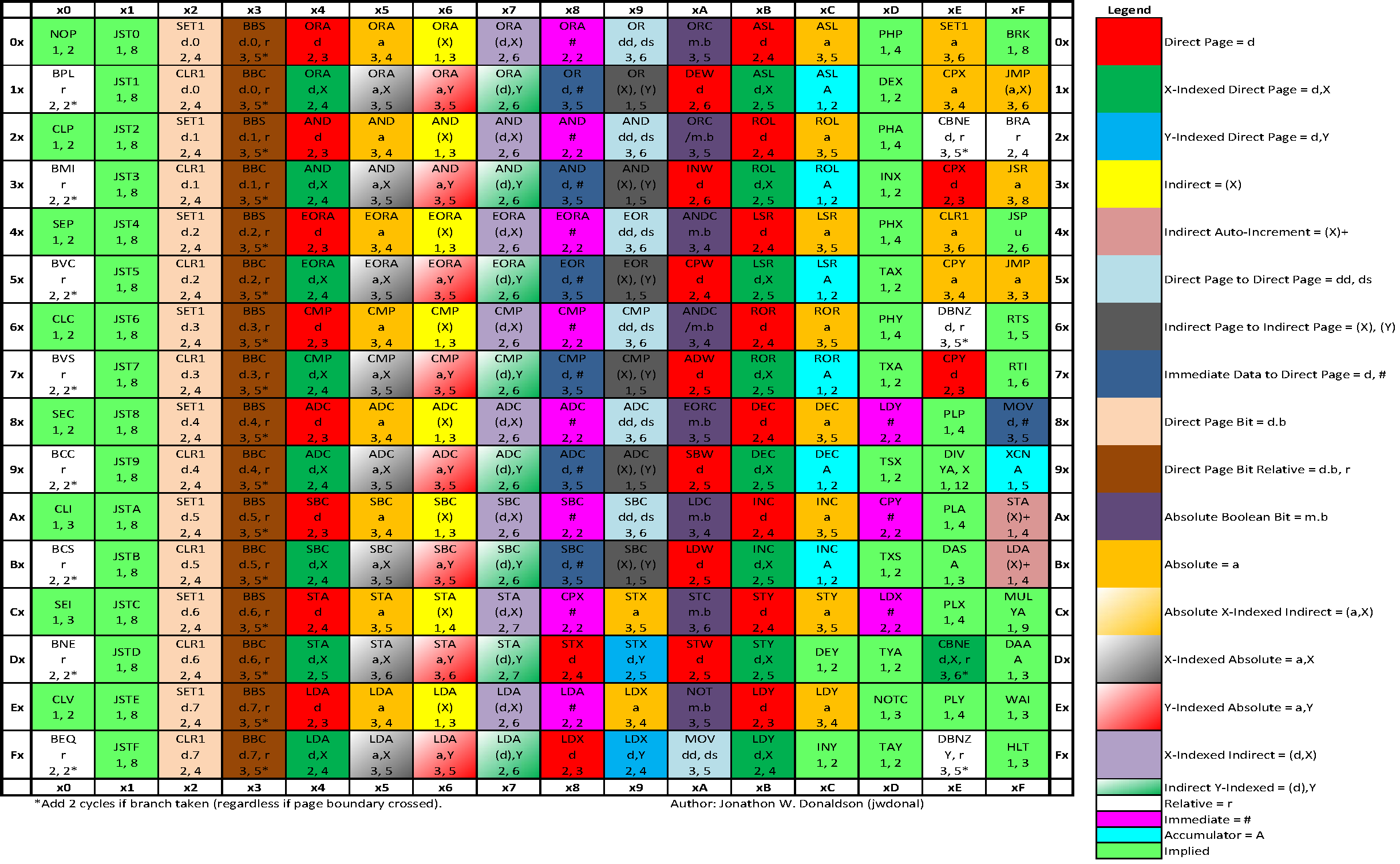

65816 opcode table

|

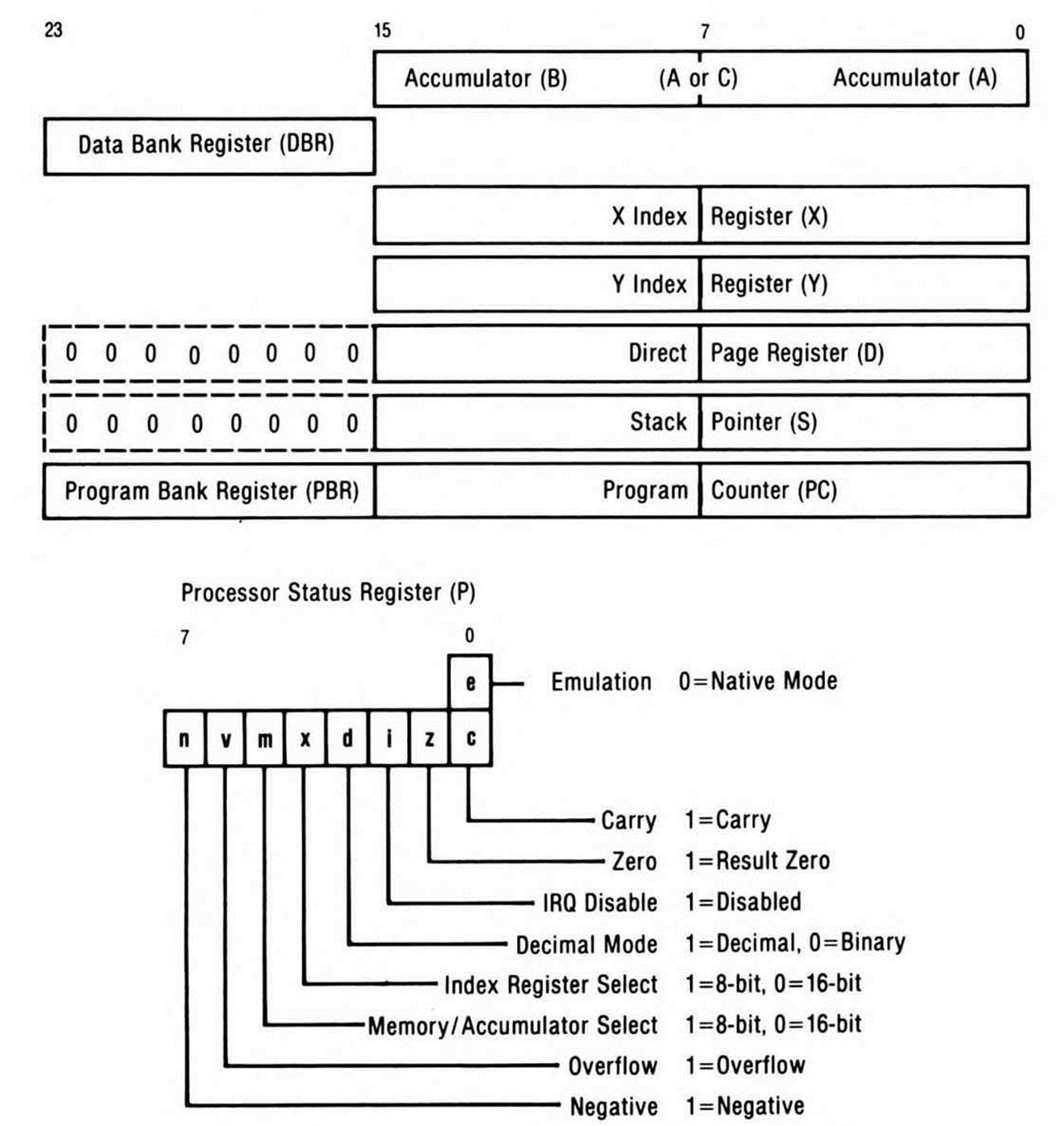

W65C816S 8/16–bit Microprocessor

9 nov 2018 · Table 5-4 Opcode Matrix The BRK instruction for the NMOS 6502 65C02 and 65C816 is actually a 2 byte instruction |

|

------------------------------------------------

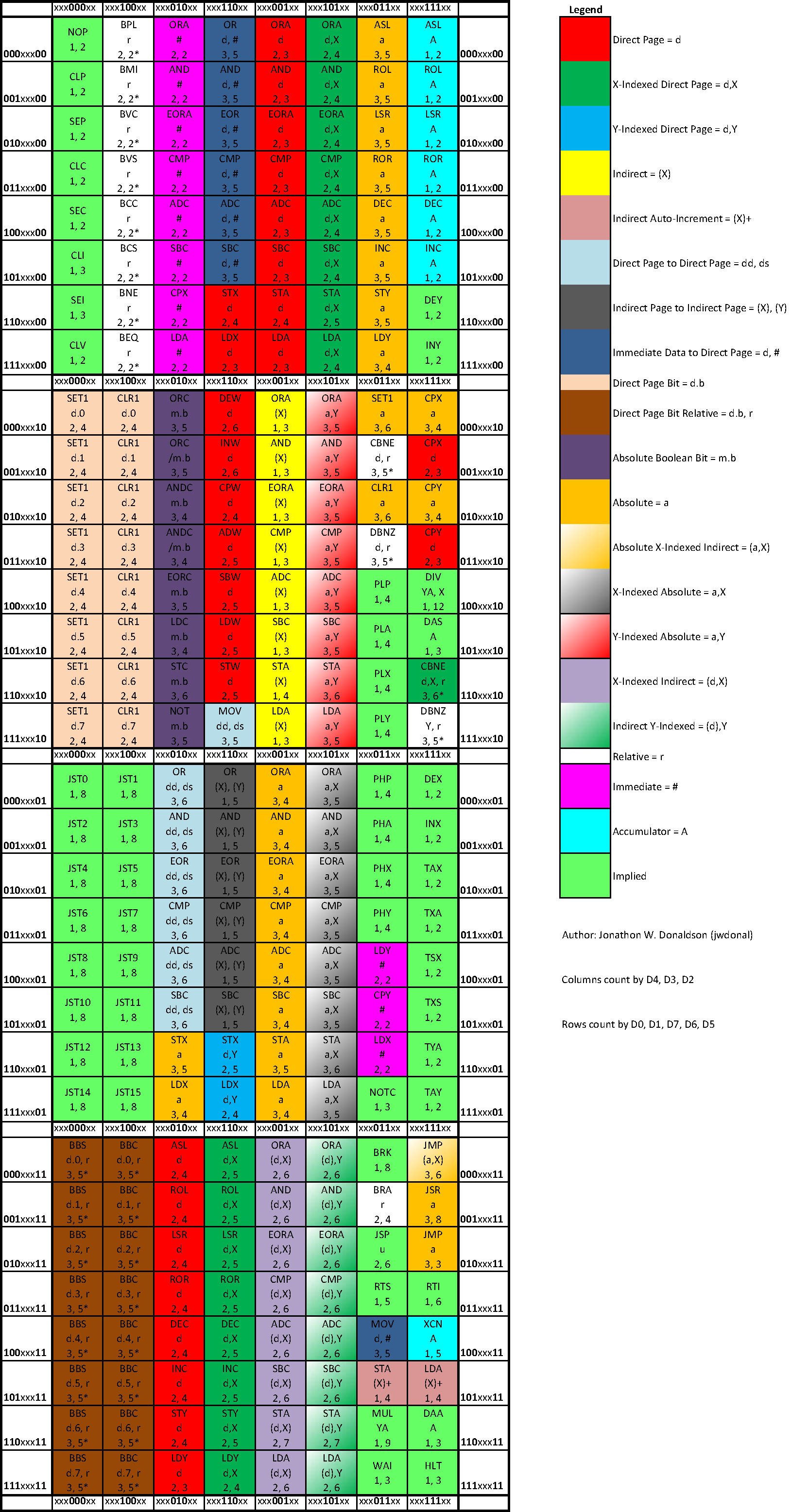

chart I have constructed that shows all the 65816 opcodes and addressing modes and the addressing modes that can be used with each opcode The numbers |

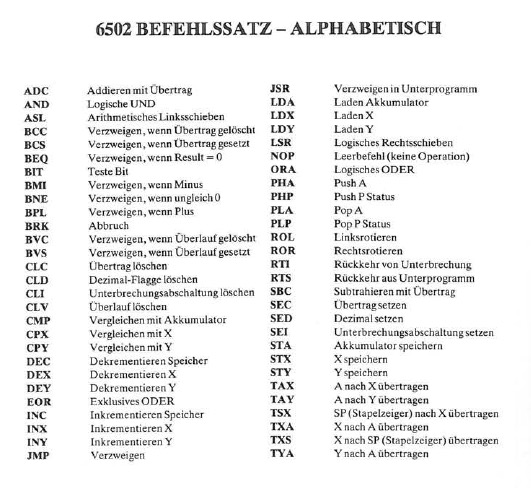

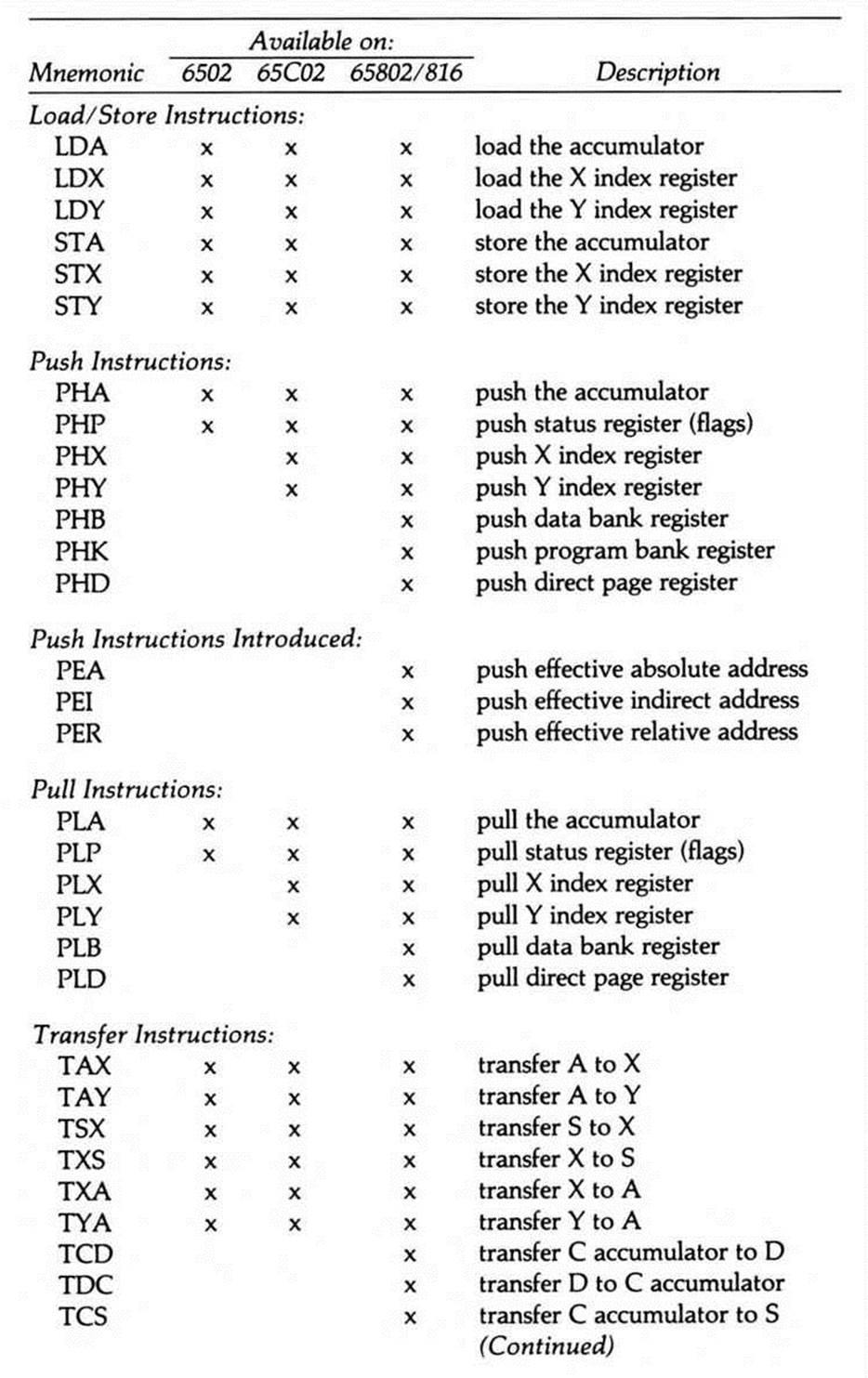

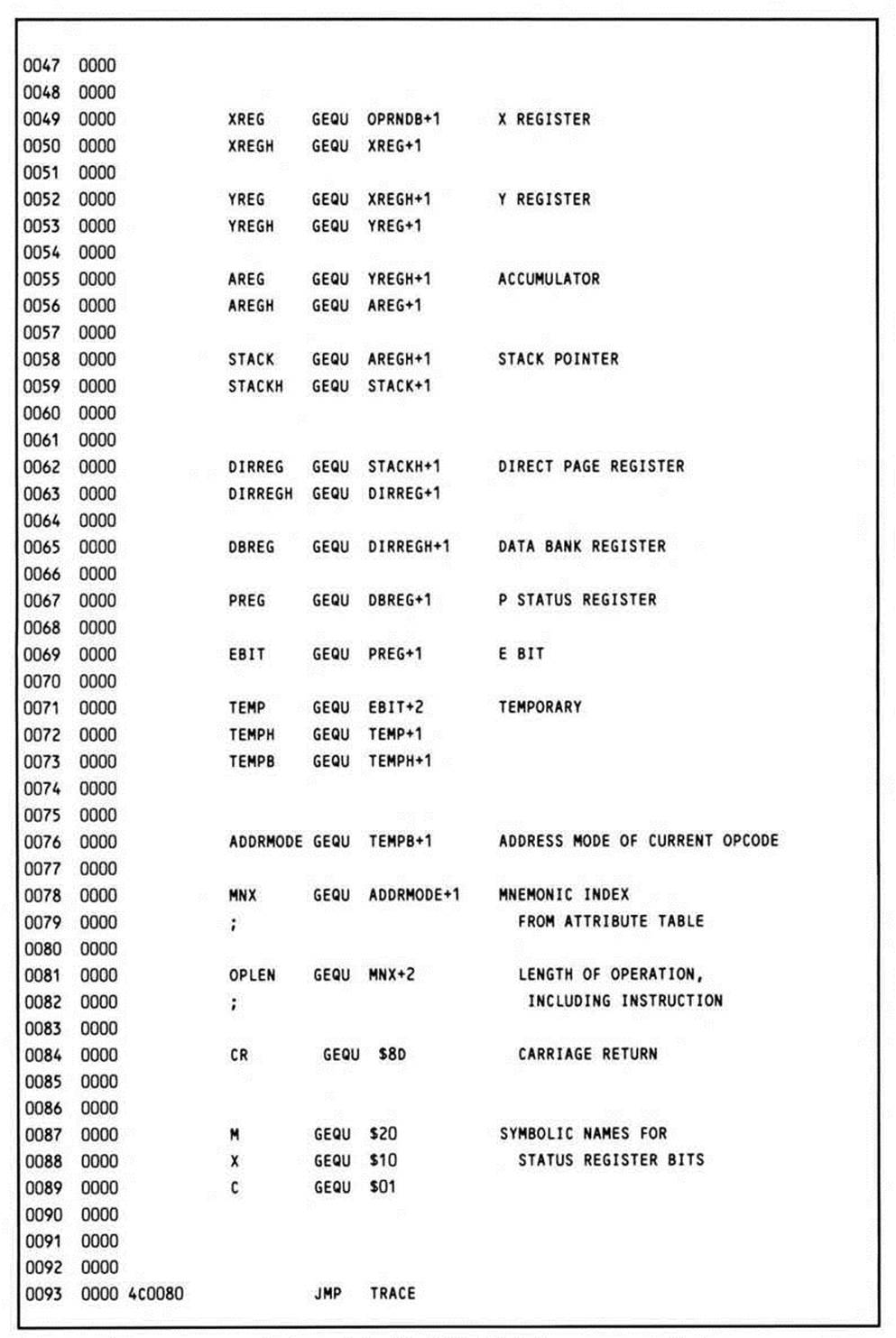

An opcode table (also called an opcode matrix) is a visual representation of all opcodes in an instruction set.

It is arranged such that each axis of the table represents an upper or lower nibble, which combined form the full byte of the opcode.

|

W65C816S Microprocessor DATA SHEET

The location of the aborted OpCode is stored as the return address in stack memory. The Abort vector address is 00FFF89 (Emulation mode) or. 00FFE8 |

|

W65C816S 8/16–bit Microprocessor

9 nov. 2018 Table 5-1 W65C816S Instruction Set-Alphabetical Sequence . ... See Programming the 65816 Manual for more information. 7.9 Indirect Jumps. |

|

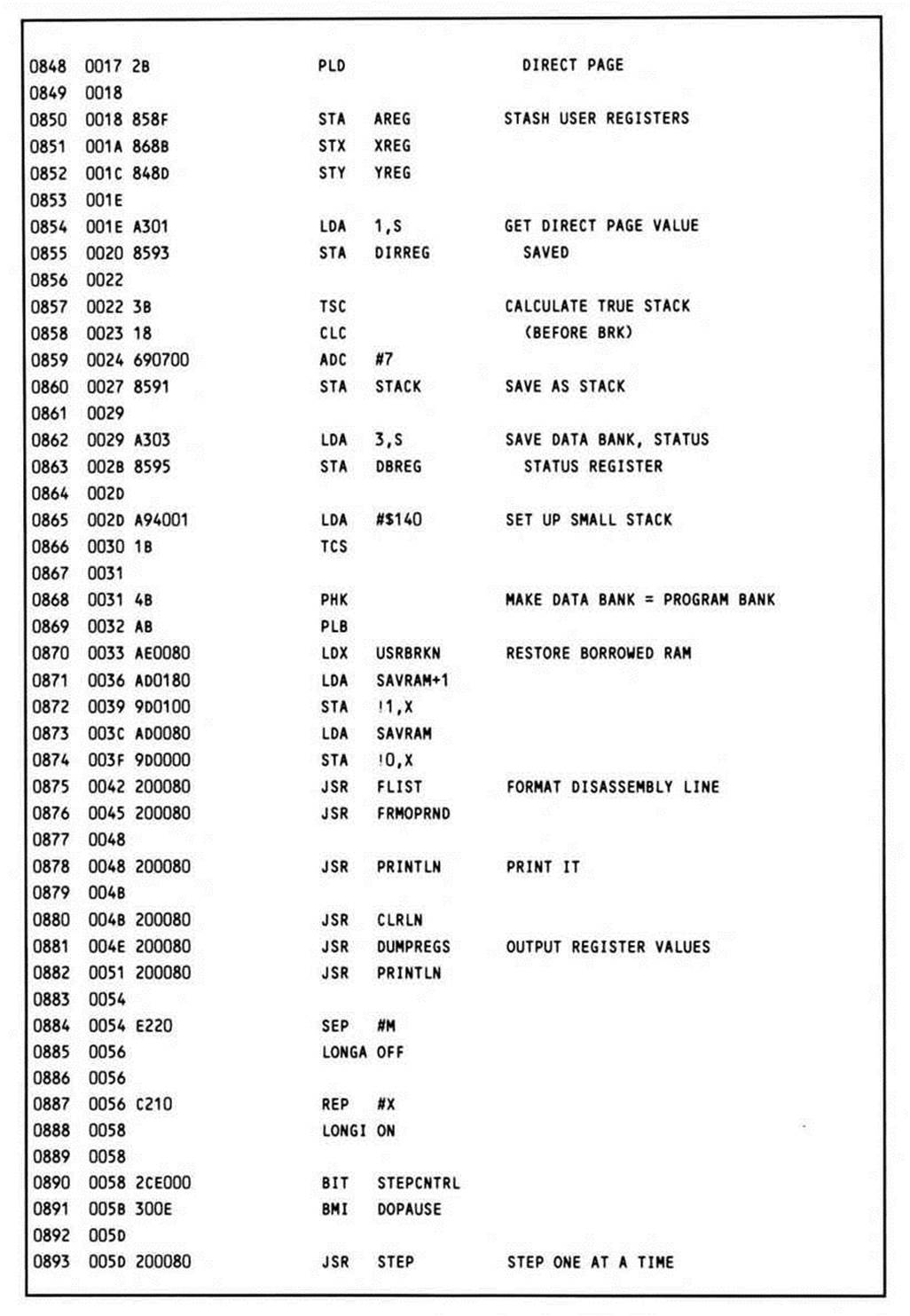

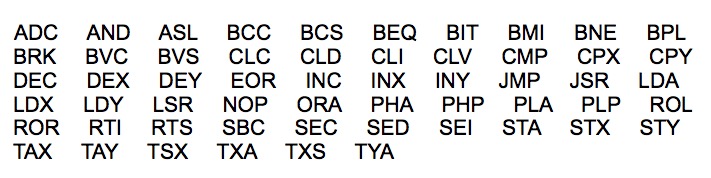

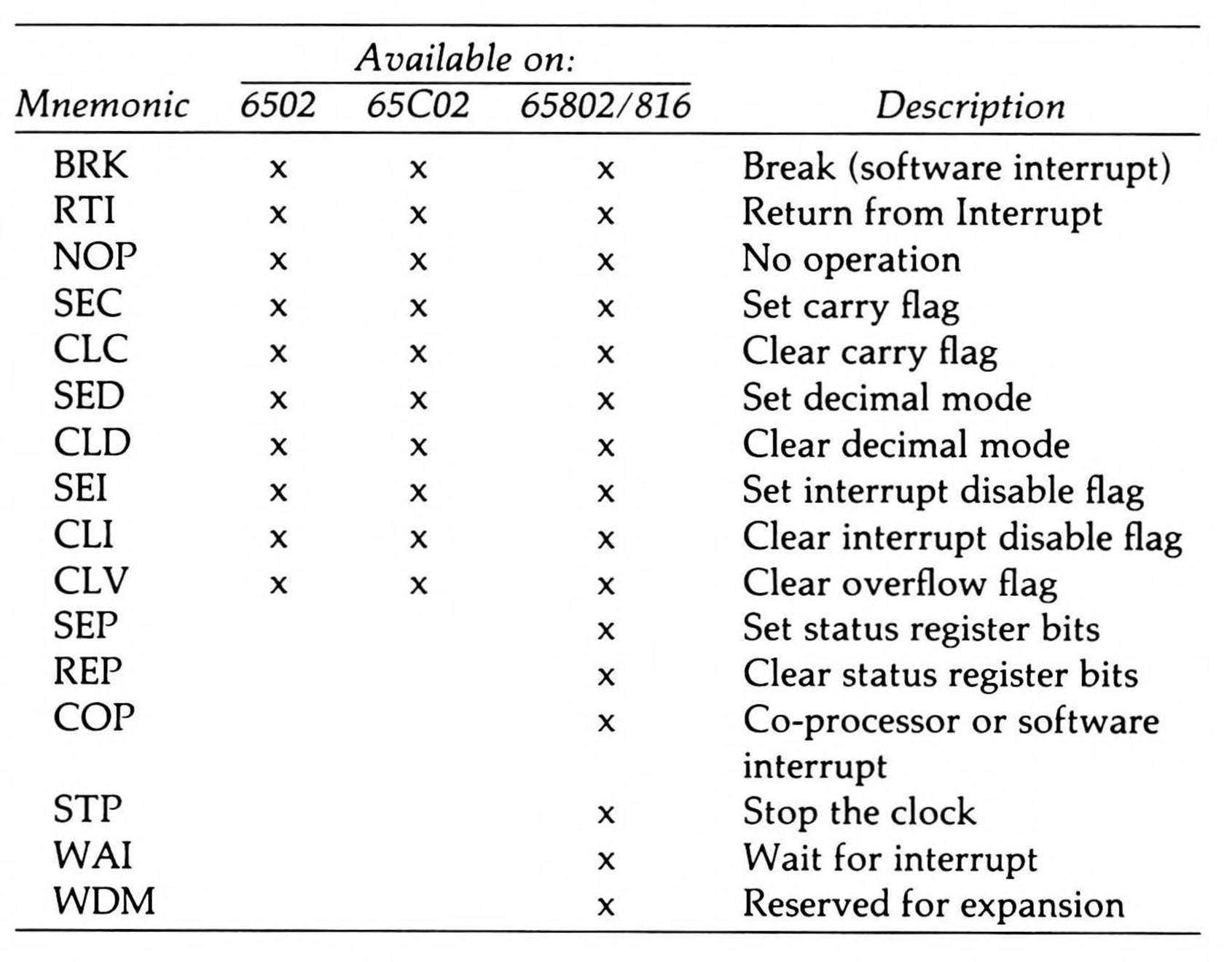

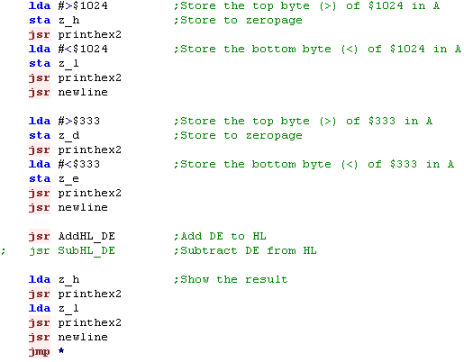

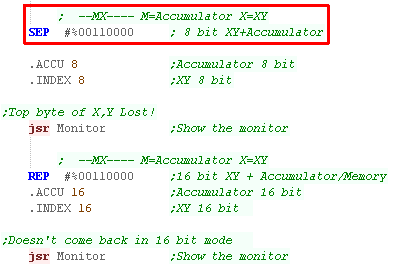

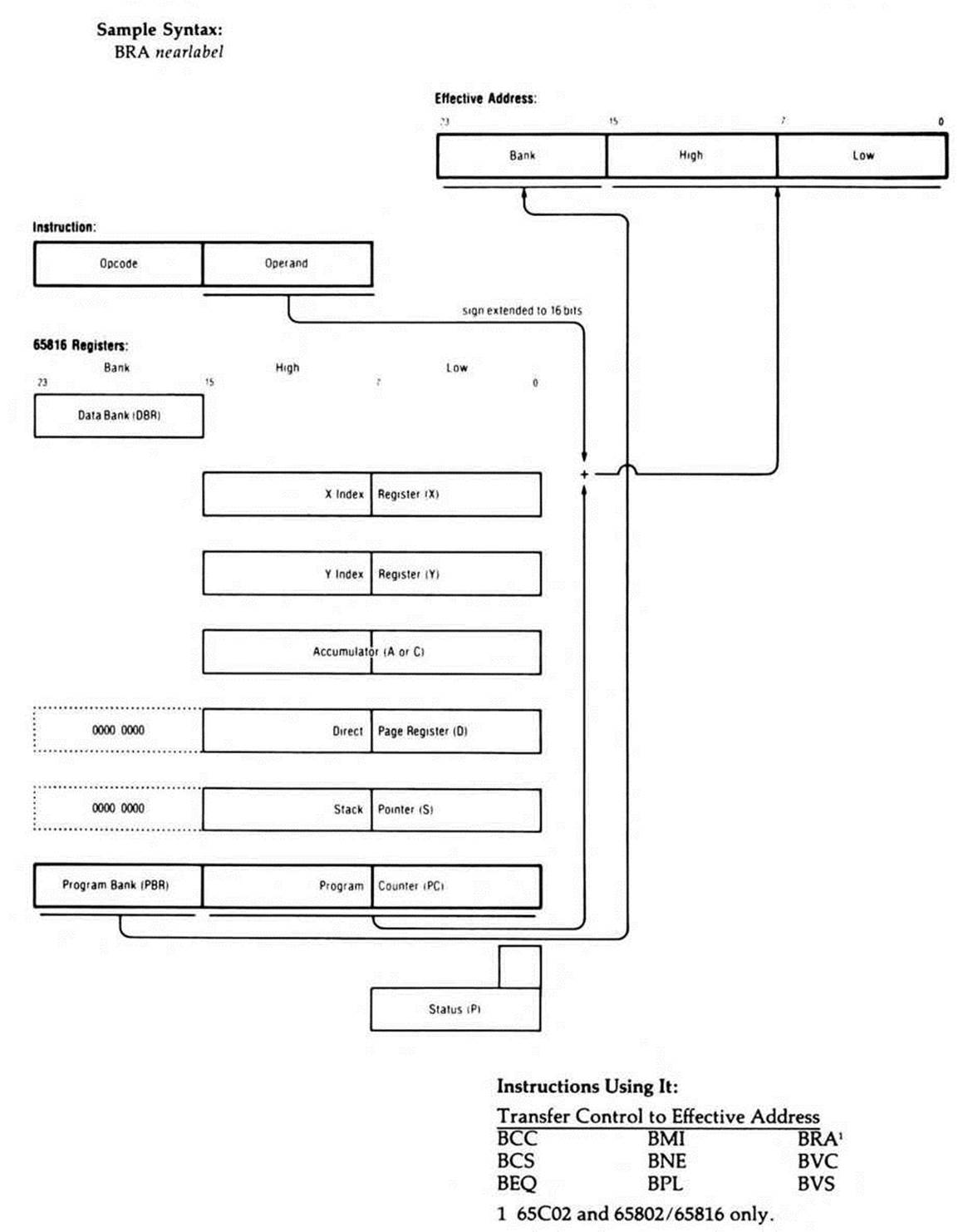

Programming the 65816

Table of Contents. 1) Chapter One . TABLE 1-6 THE EIGHT-BIT RANGE OF TWO'S-COMPLEMENT NUMBERS . ... The 65816's 256 different opcodes for example |

|

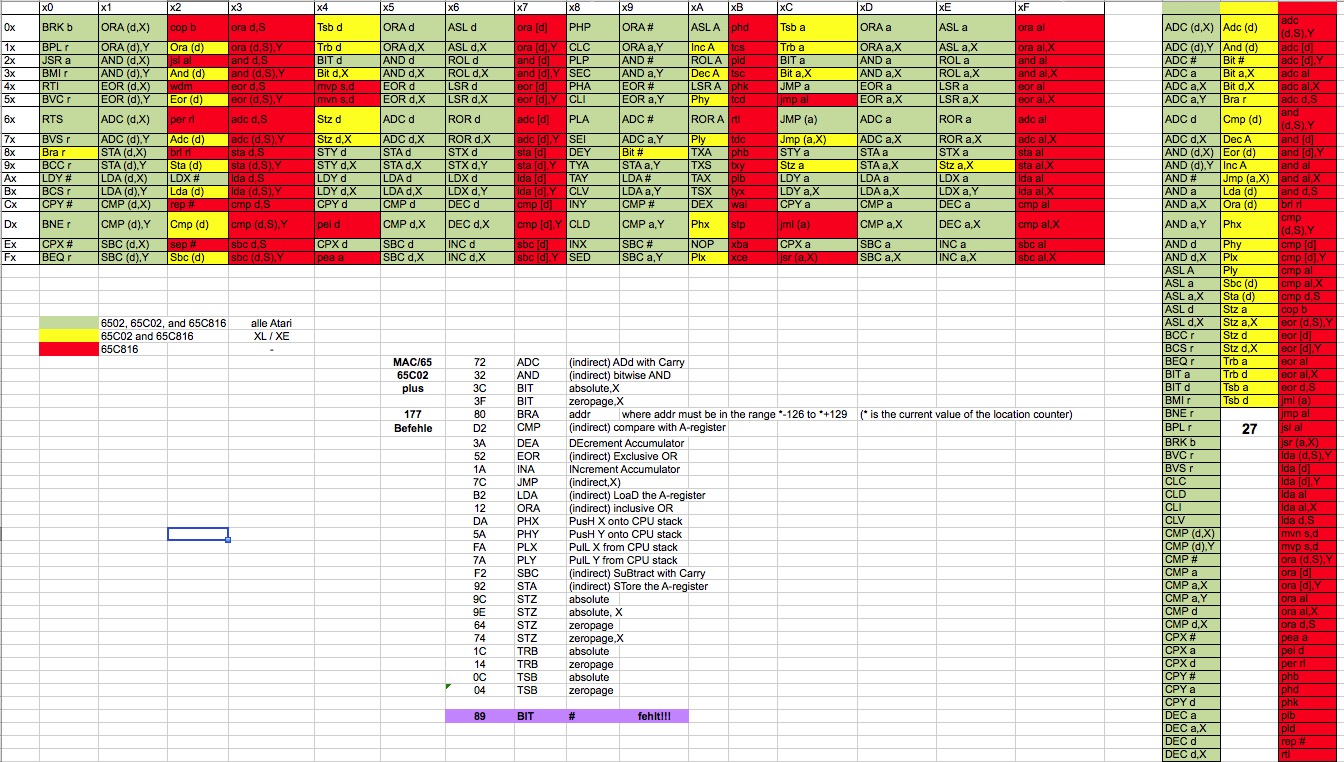

Software Development System Assembler?Linker?Librarian

6502 and 65816 instruction sets including alternate mnemonics for a number of Since macro names are added to the assembler opcode and directive table ... |

|

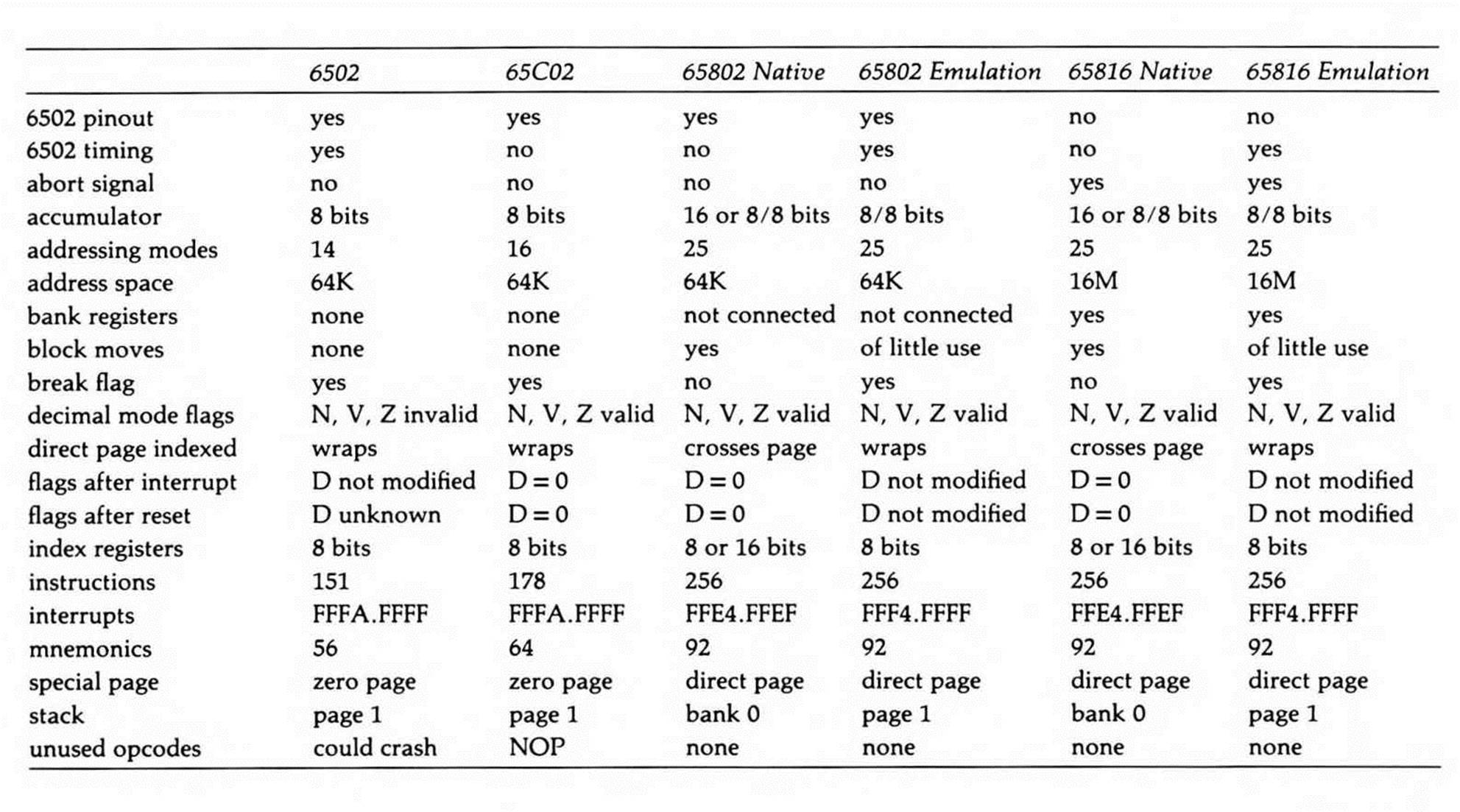

Programming the 65816 including the 6502 65C02 and the 65802

17; the instructions arranged alphabetically with descriptions and tables of opcodes and syntax |

|

Programming the 65816

TABLE 1-6 THE EIGHT-BIT RANGE OF TWO'S-COMPLEMENT NUMBERS . The 65816's 256 different opcodes for example |

|

C74-6502 Datasheet.pages

the CPU acquires certain WDC 65816 capabilities namely a 24-bit address bus. (16MB memory space) |

|

Z80 CPU User Manual

Each instance in the following revision history table reflects a change to this document Corrected the hex code for the RLCA instruction;. |

|

Wla-dx Documentation

Only the 6502 65C02 |

|

Altirra Hardware Reference Manual - VirtualDub

7 juil. 2022 65C816 opcode table. •. 800 floating I/O data bus. •. POKEY: Additional details on serial port behavior and keyboard and paddle scans. |

|

Programming the 65816 - 6502org

TABLE 1-6 THE EIGHT-BIT RANGE OF TWO'S-COMPLEMENT NUMBERS The 65816's 256 different opcodes, for example, would be difficult to remember in |

|

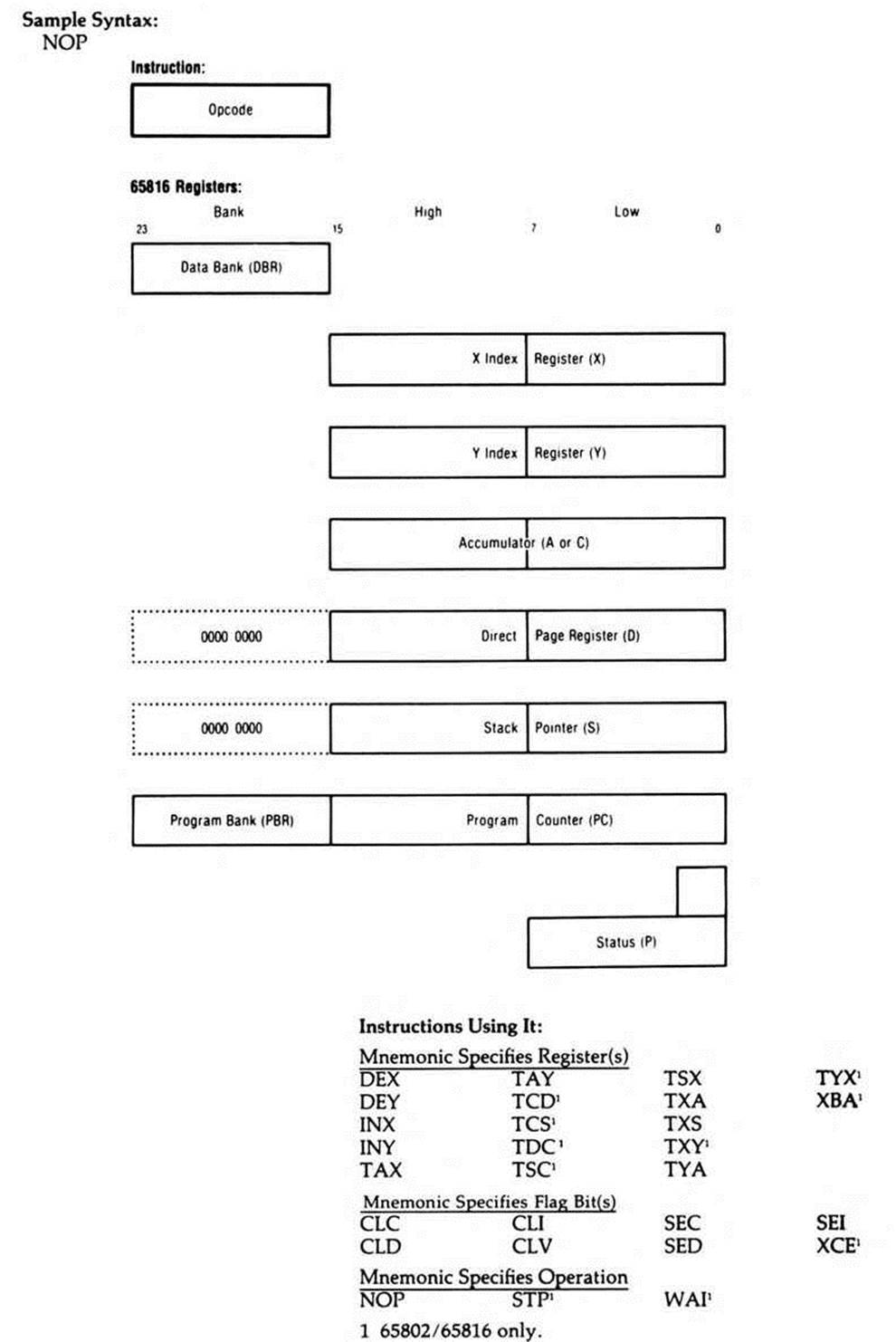

W65C816S Microprocessor DATA SHEET - Description

Internal Registers (Refer to Programming Model Table 2-2) indexed addressing, the microprocessor fetches the OpCode and the base address, The BRK instruction for the NMOS 6502, 65C02 and 65C816 is actually a 2 byte instruction |

|

W65C816S 8/16–bit Microprocessor - Western Design Center

9 nov 2018 · Table 2-1 W65C816S Microprocessor Programming Model aborted opcode is stored as the return address in stack memory The BRK instruction for the NMOS 6502, 65C02 and 65C816 is actually a 2 byte instruction |

|

AE 65816 16 bit Card - Apple-iigsinfo

Meg of memory, the full capability of the 65816 processor This Beta the microprocessor fetches the opcode and the base address, and then modifies the Table 1, W65C802 and W65C816 Mode Comparison, illustrates the features of the |

|

C74-6502 Datasheetpages - WordPresscom

opcodes The K24 Card also enables the instruction-set to be switched • Additional 65816 instructions and addressing modes Initialize SP in Task Table |

|

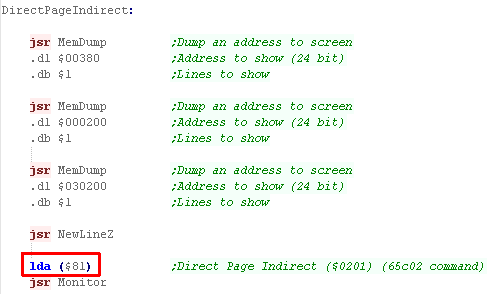

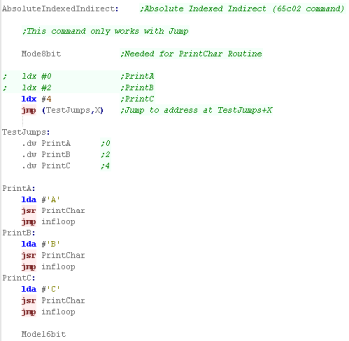

Description of 65816 flow of control instruction, jump absolute, block

28 mai 1985 · The attached document describes the 65816 flow of control instructions including branches, jumos, This description is incorrect for the Jump Absolute (opcode $4C) and the Subroutine Jump Absolute restar table |

|

NMOS 6510 Unintended Opcodes - Codebase 64

24 déc 2014 · This document does not apply to the 65C02, 65816 etc Reference chart of all ' illegal' opcodes LDA colours,x ;fetch colour from table |

|

S-C Macro

65816 microprocessors Next in Two aliases are included in the opcode table, by popular 65802/65816 Mode -- includes all of the 65C02 opcodes and |

![boards:sbc:65c816_ecb_sbc:65c816_ecb_sbc [RetroBrew Computers Wiki] boards:sbc:65c816_ecb_sbc:65c816_ecb_sbc [RetroBrew Computers Wiki]](https://patentimages.storage.googleapis.com/34/9c/9c/3bf492745e4da4/imgb0009.png)