a parallel arithmetic for hardware realization of digital filters

|

A parallel arithmetic for hardware realization of digital filters

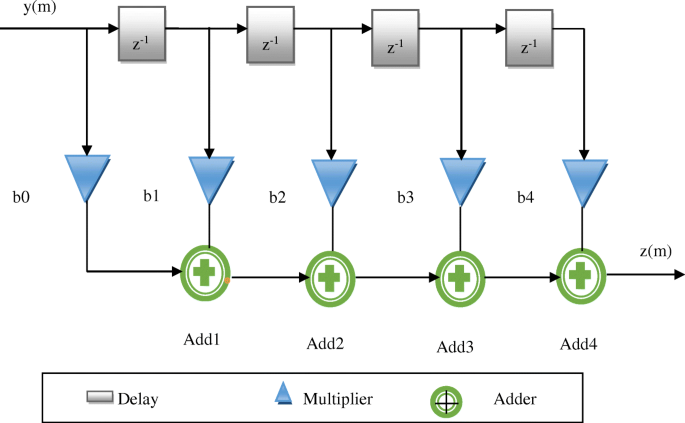

inputs and filter coefficients in parallel In this paper we present a parallel arithmetic operation for the hardware realization of digital filters The fundamental difference between the proposed method and existing methods is that the proposed method factors filter coefficients to find basic operations |

|

Hardware Realizations for Digital Signal Processing

Abstract: Distributed arithmetic structures are an alternative hardware realization to the use of conventional multipliers in the implementation of digital filters This paper compares the possible methods of partitioning the equations of a second-order digital filter for a distributed arithmetic |

|

DIGITAL FILTER STRUCTURES AND QUANTIZATION EFFECTS

Hardware implementations require significantly more logicthan fixed-point implementations; Software implementations require significantly more operations so run much more slowly on the same processor Floating point arithmetic although much harder to implement poses less of a problem to the digital filter designer than fixed point |

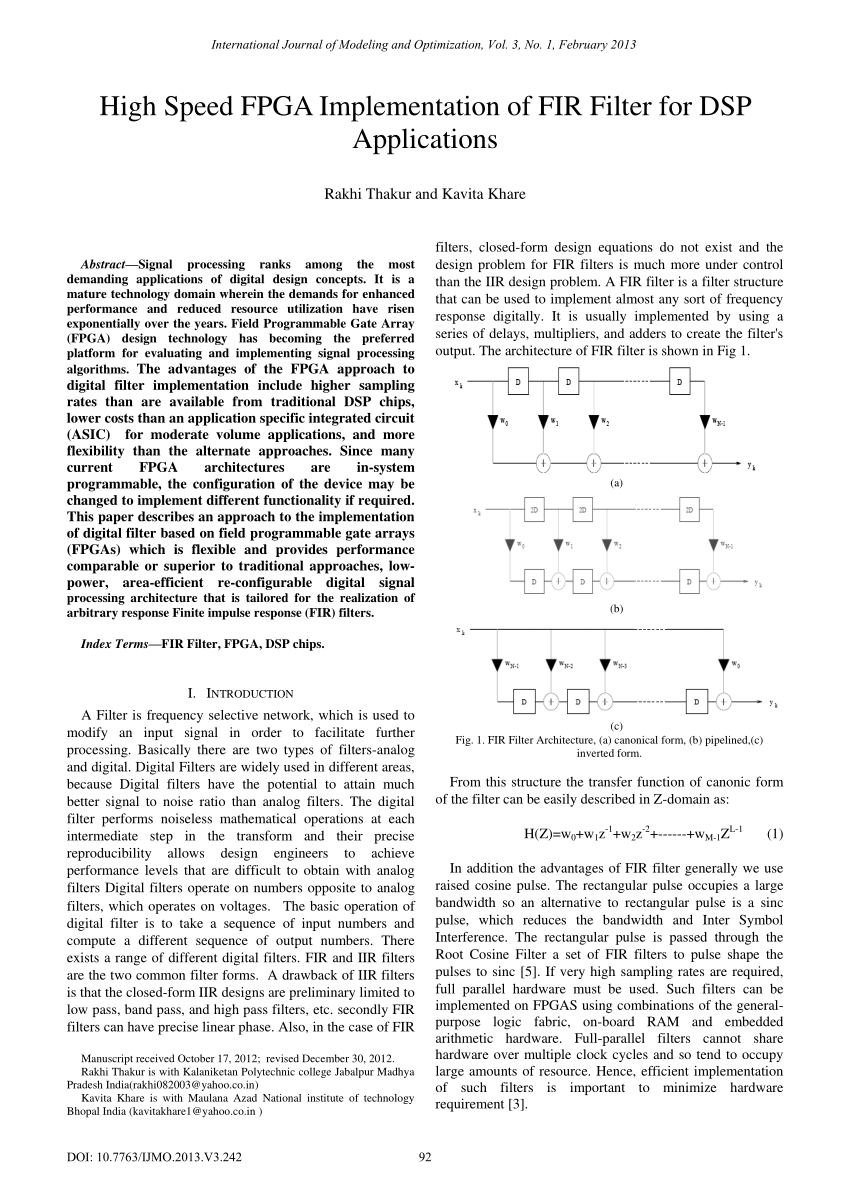

How to implement a transfer function d(z) as a “network” of primitive arithmetic operations?

The first consideration is how to implement a transfer function D(z) as a “network” of primitive arithmetic operations: add, multiply, delay. For software realizations, the network corresponds to a flowchart of the filter algorithm. For hardware realizations, the network describes the actual circuit elements and their interconnection.

Are parallel IIR filters easier to deal with?

Parallel IIR filters are a bit easier to deal with, because the issue of pairing and ordering does not arise. Jackson concluded that the total signal-to-quantization noise of the parallel form is comparable to that of the best pairing and ordering of the cascade form.

How does network structure affect the performance of a digital implementation?

For software realizations, the network corresponds to a flowchart of the filter algorithm. For hardware realizations, the network describes the actual circuit elements and their interconnection. We will see that the performance of a digital implementation is affected substantially by the choice of network structure. 2N + 1 multipliers.

|

A parallel arithmetic for hardware realization of digital filters

21 nov. 2018 Please cite this article as: C. Fan F. Li |

|

On the realization of multimemory block structure digital adaptive

DIGITAL ADAPTIVE FILTER USING DISTRIBUTED ARITHMETIC However the hardware implementation of the parallel structure is simpler and can achieve. |

|

STUDIES ON DESIGN AND IMPLEMENTATION OF LOW

A novel hardware structure for single-bit input digital filters is proposed. Arithmetic Transformation of Lattice Wave Digital Filters ......... 33. |

|

A full-parallel digital implementation for pre-trained NNs - Neural

The difficulties of parallel digital hardware imple- method for efficient implementation of digital filters uses bit-serial distributed arithmetic. |

|

High-Performance Digital Filtering on Truncated Multiply

2 déc. 2020 Moreover in the paper |

|

Towards Arithmetic-Centered Filter Design

7 mai 2021 Abstract—A hardware implementation can be defined to be faithful to the frequency specification of a linear time-invariant digital filter. |

|

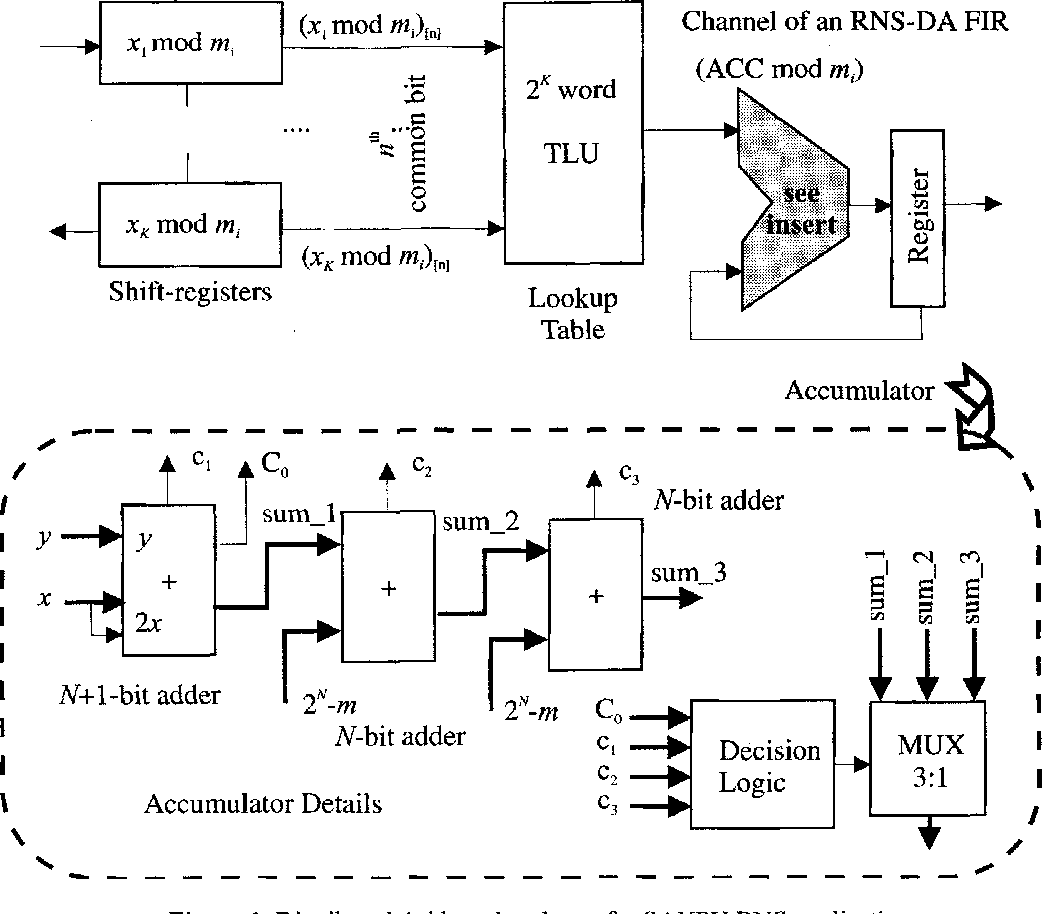

A parallel arithmetic hardware structure for recursive digital filtering

A Parallel Arithmetic Hardware Structure for for implementing recursive digital filters. ... filter implementation which combines high-speed. |

|

Implementation of High Speed FIR Filter using Serial and Parallel

Anderson “Hardware-Efficient. Distributed Arithmetic Architecture for High-Order. Digital Filters” |

|

Introduction to Digital Filters

A digital filter is a mathematical algorithm implemented in hardware and/or software that operates on a digital input signal to produce a digital output |

|

On comparing hardware implementations of fixed point digital filters

Distributed arithmetic structures are an alternative to digital filter the next step is to choose a realization ofthe ... working in parallel. |

|

An Efficient 256-Tap Parallel FIR Digital Filter - CORE

circuit hardware description language (VHDL) and verified via simulation The proposed Distributed arithmetic; DSP; Finite impulse response; LUT; MAC and parallel filters 1 Introduction Basically, digital filters are used to modify the Realization, IEEE European Conference on Circuit Theory and Design, pp 145– 148 |

|

An Efficient 256-Tap Parallel FIR Digital Filter Implementation Using

circuit hardware description language (VHDL) and verified via simulation The proposed Distributed arithmetic; DSP; Finite impulse response; LUT; MAC and parallel filters 1 Introduction Basically, digital filters are used to modify the Realization, IEEE European Conference on Circuit Theory and Design, pp 145– 148 |

|

STUDIES ON DESIGN AND IMPLEMENTATION OF LOW - DiVA

A novel hardware structure for single-bit input digital filters is proposed The proposed Arithmetic Transformation of Lattice Wave Digital Filters 33 2 1 Hence, a recursive algorithm is required for realization of an IIR filter Recursive filters A special case of digit-serial processing is bit-parallel processing A digit- |

|

DIGITAL FILTERS - SMT

digital filters, which are filters suitable to process sampled a DSP, floating-point arithmetic is usually available; there- specific hardware or lower cost DSPs, fixed-point arith- realization of the parallel adaptor has internal multipliers |

|

REALIZATION OF FIR FILTER USING MODIFIED - ResearchGate

Index terms: Distributed Arithmetic, Finite Impulse Response , Field realization of FIR digital filters with less power consumption has become Systolic design architectures represent an efficient hardware implementation for computation- exploiting high-level of concurrency using pipelining or parallel processing or both |

|

Text

HARDWARE IMPLEMENTATION OF DIGITAL FILTERS Saleem G Zoughbi : " implement recursive and non-recursive digital filters In other words, it is 1 3 4 Parallel realization 1 4 Digital 2 2 1 The arithmetic unit 2 2 2 |

|

On comparing hardware implementations of fixed point digital filters

Distributed arithmetic structures are an alternative to the use of conventional mentations of digital filters This paper compares digital filter, the next step is to choose a realization ofthe tations which are highly parallel and do not fit into the |

|

Applications of distributed arithmetic to digital signal processing: a

in circuit design, but off-the-shelf hardware often can Tam and Hawkins [22], Arjmand and The April 1975 special digital signal pro- in a parallel fashion is exactly the same as the time re- a realization of the 9-multiplier configuration of Figure 7 we have reduced the Distributed Arithmetic Filters," IEEE Trans on Cir- |

![PDF] Hardware Realization of FIR Filter Implementation through PDF] Hardware Realization of FIR Filter Implementation through](https://media.springernature.com/original/springer-static/image/chp%3A10.1007%2F978-3-030-24063-9_6/MediaObjects/477841_1_En_6_Fig1_HTML.png)

![PDF] An Efficient 256-Tap Parallel FIR Digital Filter PDF] An Efficient 256-Tap Parallel FIR Digital Filter](https://media.springernature.com/lw685/springer-static/image/art%3A10.1186%2Fs43067-020-00025-4/MediaObjects/43067_2020_25_Fig5_HTML.png)

![PDF] RNS implementation of FIR filters based on distributed PDF] RNS implementation of FIR filters based on distributed](https://upload.wikimedia.org/wikipedia/commons/thumb/c/c3/Biquad_filter_DF-I.svg/400px-Biquad_filter_DF-I.svg.png)

![PDF] An Efficient 256-Tap Parallel FIR Digital Filter PDF] An Efficient 256-Tap Parallel FIR Digital Filter](https://data01.123dok.com/thumb/z1/2e/jddy/Pki4ZiPT5VIqTD1so/cover.webp)

![PDF] Hardware-efficient distributed arithmetic architecture for PDF] Hardware-efficient distributed arithmetic architecture for](https://media.springernature.com/original/springer-static/image/chp%3A10.1007%2F978-981-15-5089-8_14/MediaObjects/495133_1_En_14_Fig2_HTML.png)

![PDF] Efficient bit-level systolic array implementation of FIR and PDF] Efficient bit-level systolic array implementation of FIR and](https://0.academia-photos.com/attachment_thumbnails/33357590/mini_magick20190403-6847-1mtux96.png?1554330640)