"cadence virtuoso" training

How long does it take to become Cadence certified?

Length: 2 Days (16 hours) Become Cadence Certified In this course, you learn the basic techniques for working with designs in the Virtuoso® Studio Layout Suite environment. You create and edit cell-level designs. You create and place instances to build a hierarchy for custom physical designs.

What is cadence online training?

Our free Online Training Course Library ensures you get the training you need at times that are convenient for you. Online Training is delivered over the web—letting you proceed at your own pace—anytime, anywhere. With Cadence Online Training, you can sharpen your skills easily...and often.

What is Cadence Virtuoso?

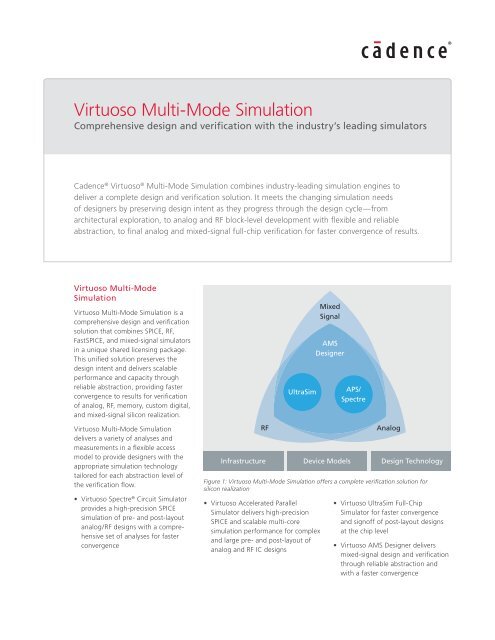

11. • Cadence Virtuoso. • It is a Circuit simulator tool which provides capabilities of designing the circuit, testing of circuit, designing of layout and its verification. • It has a feature named Analog Design Environment (ADE).

What is the cadence ® retool-to-work program?

The Cadence ® Retool-to-Work Program is a community outreach program offered to qualified candidates who need to update their design skills. Learn more about the training and learning opportunities for Cadence customers. Cadence provides online and in-person training along with training blogs and webinars.

Course Description

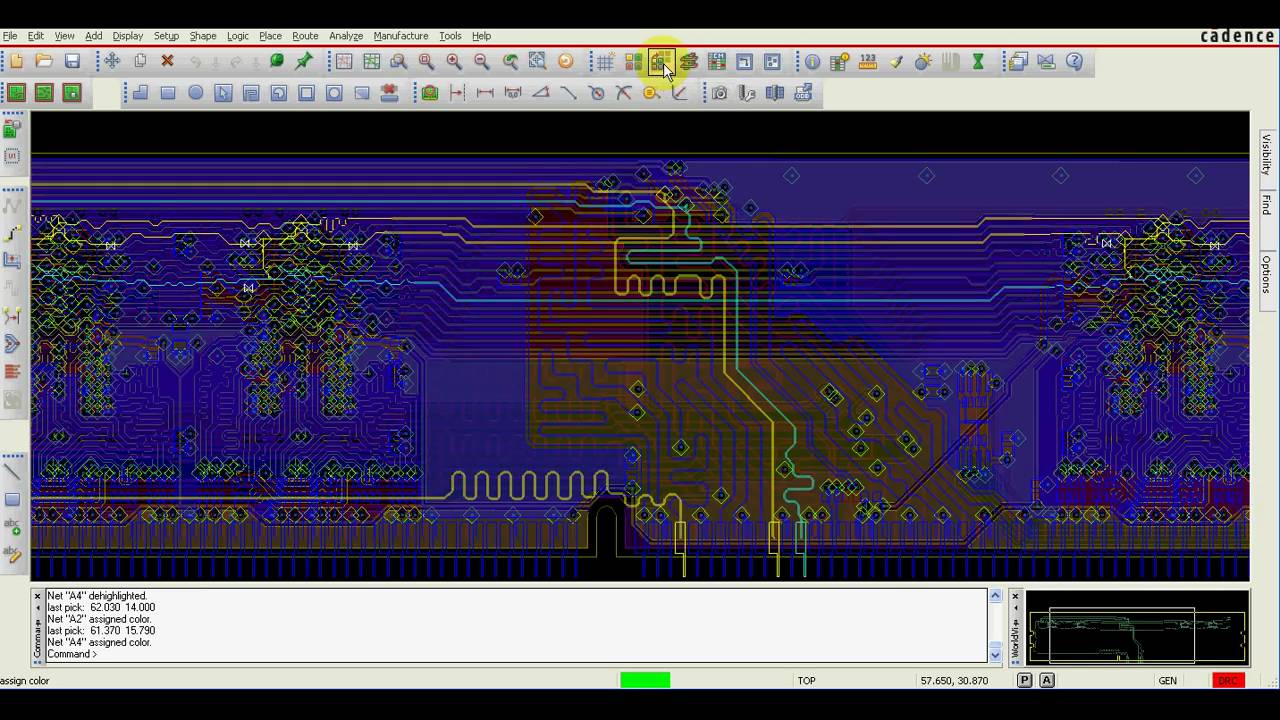

In this course, you learn the basic techniques for working with designs in the Virtuoso®Studio Layout Suite environment. You create and edit cell-level designs. You create and place instances to build a hierarchy for custom physical designs. You explore the basics of the user interface and the user-interface assistants, which help select, navigate,

Learning Objectives

After completing this course, you will be able to: 1. Navigate with the user interface 2. Use design assistants and workspaces 3. Edit layout designs 4. Use path stitching 5. Edit the properties of objects 6. Create a transistor manually to exercise the more common commands for creating and editing 7. Create and edit a design-rule-correct layout by

Modules in This Course

The Design EnvironmentThe User InterfaceBasic and Advanced Layout CommandsDesign Rule Driven Editing, Hierarchical Design, and XStream In and Out cadence.com

Audience

Analog/Mixed Signal EngineersIC DesignersLayout DesignersPhysical Layout Designers cadence.com

Prerequisites

Before taking this course, you need to have: 1. Experience with layout design 2. Knowledge of schematic symbols and MOS devices 3. A basic knowledge of UNIX/Linux cadence.com

Related Courses

Virtuoso Layout Pro: T1 Environment and Basic Commands (L)(opens in a new tab)Virtuoso Layout Pro: T2 Create and Edit Commands (L)(opens in a new tab) cadence.com

Cadence Virtuoso: Introduction

Know How to Build the Perfect Layout: Cadence Virtuoso Layout Pro Training Series

Cadence Virtuoso tool for the design of CMOS inverter Cadence tutorial DC & Transient Analysis

|

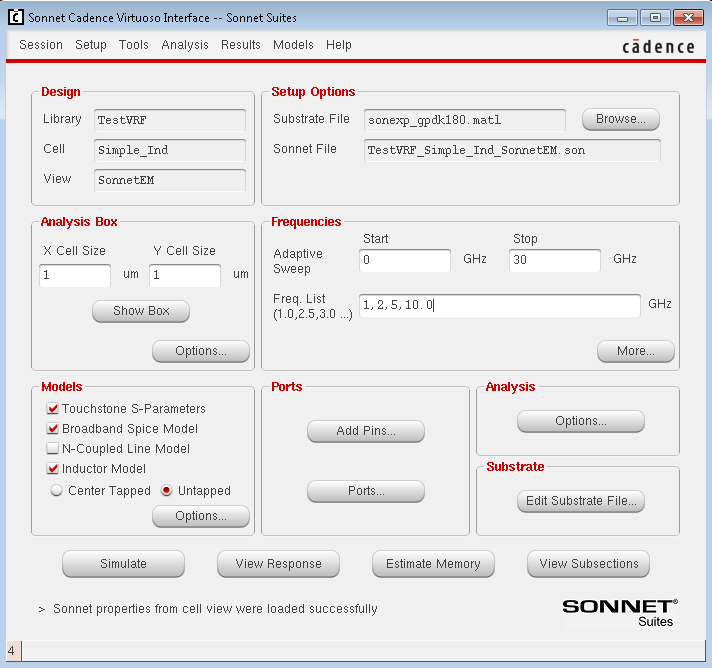

Sonnet/Virtuoso Interface Training

Sonnet Cadence Virtuoso Interface Flowchart cvbridge. Interface. Layout Cell View. SonnetEM. Cell View. Project Editor. EM Simulation. Response. Data. |

|

Training Courses

using either a Synopsys Custom Compiler or Cadence Virtuoso design tool flow (two courses) EUROPRACTICE training courses use realistic design examples and ... |

|

Cadence PCell Designer Datasheet

It provides an intuitive GUI within the. Cadence Virtuoso® Layout Suite and Virtuoso Schematic support for support and www.cadence.com/training for training. |

|

Cadence Virtuoso Digital Implementation

Cadence Virtuoso Digital Implementation. Timing-driven digital block the flexibility of training at your own computer via the Internet. • Cadence Online ... |

|

CND101: Introduction to Analog Design

This lab is a general introductory tutorial on Cadence Virtuoso which is the simulation tool we will use for the rest of the training. The official program |

|

Cadence Modus DFT Software Solution

Cadence Virtuoso® Liberate™ solutions. • Hierarchical SoC test pattern and www.cadence.com/training for training. |

|

Cadence SiP Design

Cadence SiP solutions seamlessly integrate with. Cadence Encounter® technology for die abstract co-design Cadence Virtuoso® flexibility of training at your ... |

|

Qualitative Data Augmentation for Performance Prediction in VLSI

15 февр. 2023 г. requirement for training good and accurate machine learning models for the ... Cadence Virtuoso for current reference circuit data. Figure 6 ... |

|

Cadence Virtuoso Setup

17 сент. 2017 г. This is a guide to connecting to your CCV account and setting up Cadence Virtuoso tools. This semester we are also using a 45nm freePDK45 ... |

|

EMX Planar 3D Solver

courses allow you the flexibility of training at your own computer via the and www.cadence.com/training for training. Figure 5: Interface to Cadence Virtuoso. |

|

Sonnet/Virtuoso Interface Training

Sonnet Cadence Virtuoso Interface Flowchart cvbridge. Interface. Layout Cell View. SonnetEM. Cell View. Project Editor. EM Simulation. Response. |

|

Cadence Virtuoso Tutorial

Cadence Virtuoso Tutorial version 6.1. University of Southern California. Last Update: Oct 2015. EE209 – Fall 2015. Page 2. Table of Contents. |

|

Hands-on-Training On VLSI Circuit Design (Analog/Digital) Using

11 juin 2015 VLSI Layout design (using Cadence Virtuoso Layout Editor). • Analog Environment Simulation. • Layout versus schematic simulation(LVS). |

|

Training Courses

using either a Synopsys Custom Compiler or Cadence Virtuoso design tool flow (two courses). Advanced Analogue IC Design . |

|

Cadence PCell Designer

Cadence Virtuoso® Layout Suite and Virtuoso Schematic allow you the flexibility of training at your own computer via the internet. |

|

EMX Planar 3D Solver

Seamless interface to Cadence Virtuoso® Custom IC. Design Platform courses allow you the flexibility of training at your own computer via the internet. |

|

On-chip learning in a conventional silicon MOSFET based Analog

1 juil. 2019 entire system on SPICE circuit simulator we obtain high training and test accuracy on the ... nology node on Cadence Virtuoso circuit simu-. |

|

Cadence

Integrated with Cadence Virtuoso® full-custom design allow you the flexibility of training at your own computer over the Internet. |

|

Cadence Modus DFT Software Solution

simulators and Cadence Virtuoso® Liberate™ solutions. ? Hierarchical SoC test pattern courses allow you the flexibility of training at your own. |

|

Cadence Virtuoso Schematic Design and Circuit Simulation Tutorial

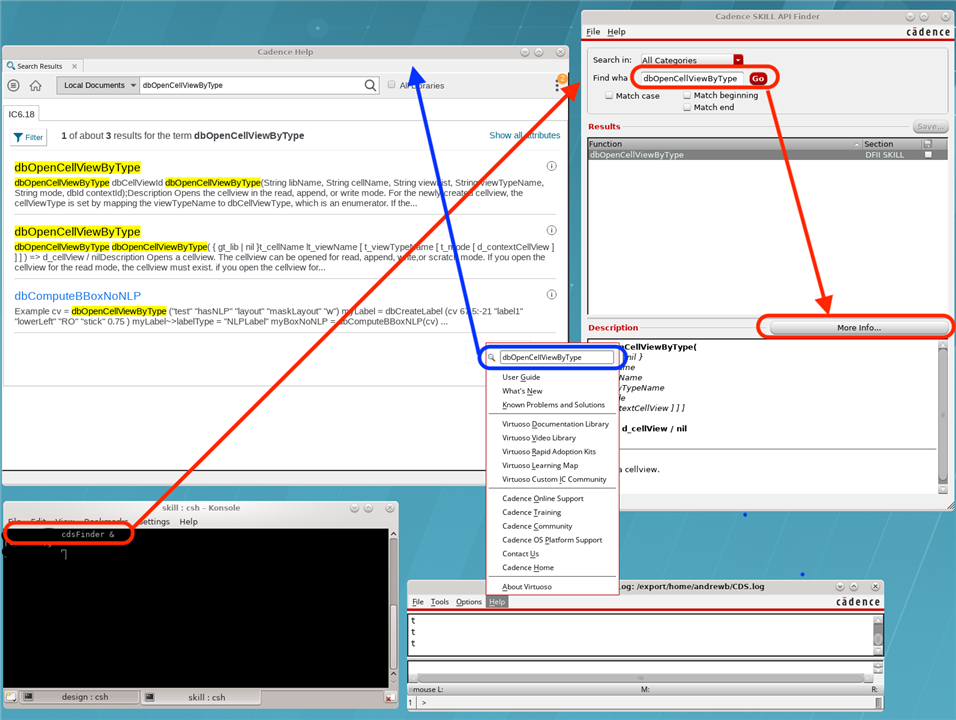

9 sept. 2016 It will also walk you through simulating the circuits in Spectre. In order to launch Cadence Virtuoso (either on the instructional machines or ... |

|

Online Training Courses Check out our Course Catalog - Cadence

85040EC Virtuoso Visualization and Analysis Online Custom IC/Analog/RF Design (CIC) Check out our Course Catalog https://www cadence com/training html |

|

Custom Design with Virtuoso Technology (CIC) - Cadence

Custom Design with Virtuoso Technology (CIC) Check out our Course Catalog: https://www cadence com/training html FREE Training Byte videos |

|

Cadence Virtuoso Tutorial - University of Southern California

which virtuoso /usr/usc/cadence/2009/IC610/tools/dfII/bin/virtuoso B Go to your home directory, open your cshrc file and add the following lines at the end of |

|

Cadence Virtuoso Schematic Design and Circuit Simulation Tutorial

9 sept 2016 · At this point we are ready to design our first schematic Creating an inverter using transistors from the PDK library Throughout the course, you will |

|

Hands-on-Training On VLSI Circuit Design (Analog - NIT Silchar

11 jui 2015 · VLSI Layout design (using Cadence Virtuoso Layout Editor) • Analog Environment Simulation • Layout versus schematic simulation(LVS) |

|

Sonnet/Virtuoso Interface Training - Sonnet Software

Sonnet Cadence Virtuoso Interface Flowchart cvbridge Interface Layout Cell View SonnetEM Cell View Project Editor EM Simulation Response Data |

|

TUTORIAL CADENCE DESIGN ENVIRONMENT

Layout Edition and Verification with Cadence Virtuoso and Diva The above approach is useful for learning the design rules and layers available for a certain |

|

Cadence Tutorial A: Schematic Entry and Functional Simulation

These may be helpful in learning Cadence, but because of differences in the For more information about Cadence Virtuoso or the ADE tool, see the manuals |

|

Virtuoso Analog Design Environment datasheet - FlowCAD

The Cadence® Virtuoso® Analog Design Environment is the analog design The Virtuoso custom design platform Reduces learning curve with intuitive, |

|

Mixed-Signal IC Design Kit Training Manual

Verification Post-Layout Simulation for Mixed-Signal Design Agenda Mixed- Signal IC Design Kit • Cadence – Affirma:VHDL/Verilog, Verilog-A, Spectre |

![Tutorial on Cadence Virtuoso - IISC - [PDF Document] Tutorial on Cadence Virtuoso - IISC - [PDF Document]](https://imgv2-2-f.scribdassets.com/img/document/408450832/original/2997c70ed7/1614763731?v\u003d1)

![Tutorial on Cadence Virtuoso - IISC - [PDF Document] Tutorial on Cadence Virtuoso - IISC - [PDF Document]](https://user-images.githubusercontent.com/27668656/55213132-9e642280-51af-11e9-8ed1-b9fe4fbab234.png)

![Cadence Virtuoso Spectre - Virtuoso_mmsim - [PDF Document] Cadence Virtuoso Spectre - Virtuoso_mmsim - [PDF Document]](https://img.yumpu.com/6405649/1/500x640/ece-128-cadence-tutorial-using-cadence-encounter-digital-.jpg)