chisel language tutorial

|

Chisel Manual

Sep 24 2012 · A sep-arate Chisel tutorial document provides a gentle in-troduction to using Chisel and should be read first This manual provides a comprehensive overview and specification of the Chisel language which is re-ally only a set of special class definitions predefined objects and usage conventions within Scala |

|

Chisel Tutorial

This document is a tutorial introduction to Chisel (Constructing Hardware In a Scala Embedded Language) Chisel is a hardware construction language embedded in the high-level programming language Scala At some point we will provide a proper reference manual in addition to more tutorial examples In the mean-time this document along with a lot of |

How does chisel test a circuit?

Testing is a crucial part of circuit design, and thus in Chisel we provide a mechanism for testing circuits by providing test vectors within Scala using tester method calls which binds a tester to a module and allows users to write tests using the given debug protocol. In particular, users utilize:

What languages is chisel available in?

It is available in English, Chinese, Japanese, and Vietnamese. For a deeper introduction to key concepts in Chisel see the Explanations. The API Documentation gives the detailed reference for the Chisel source code. The Resources provides links to other useful resources for learning and working with Chisel.

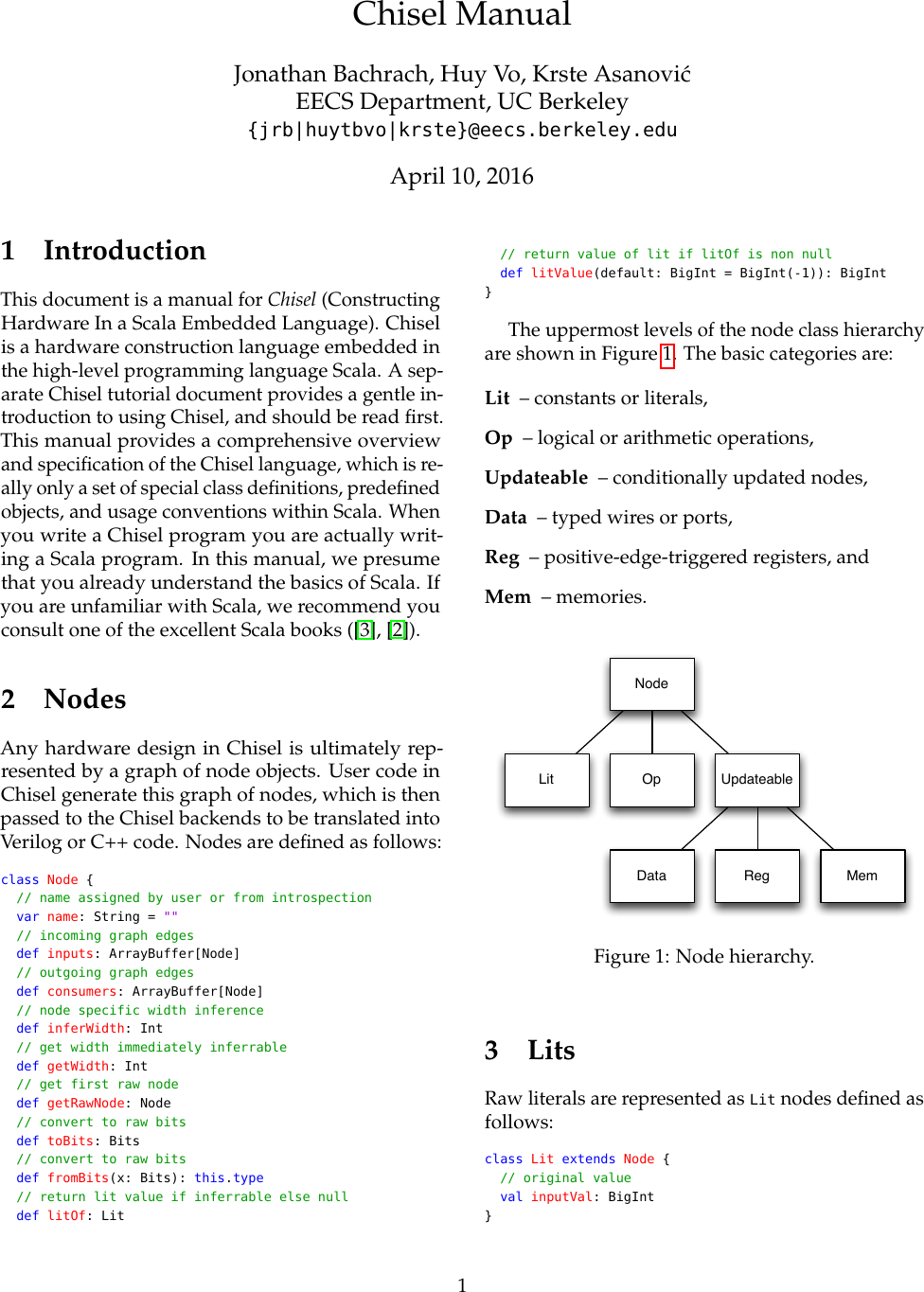

1 Introduction

This document is a tutorial introduction to Chisel (Constructing Hardware In a Scala Embedded Language). Chisel is a hardware construction language embedded in the high-level programming language Scala. At some point we will provide a proper reference manual, in addition to more tutorial examples. In the mean-time, this document along with a lot of

2 Hardware expressible in Chisel

The initial version of Chisel only supports the expression of synchronous RTL (Register-Transfer Level) designs, with a single common clock. Synchronous RTL circuits can be expressed as a hierarchical compo-sition of modules containing combinational logic and clocked state elements. Although Chisel assumes a single global clock, local clock gating

3 Datatypes in Chisel

Chisel datatypes are used to specify the type of values held in state elements or flowing on wires. While hardware designs ultimately operate on vectors of binary digits, other more abstract representations for values allow clearer specifications and help the tools generate more optimal circuits. In Chisel, a raw col-lection of bits is represented

4 Combinational Circuits

circuit is represented as a graph of nodes in Chisel. Each node is a hardware operator that has zero or more inputs and that drives one output. A literal, introduced above, is a degenerate kind of node that has no inputs and drives a constant value on its output. One way to create and wire together nodes is using textual expressions. For example, w

5 Builtin Operators

Chisel defines a set of hardware operators for the builtin types. inst.eecs.berkeley.edu

5.1 Bitwidth Inference

Users are required to set bitwidths of ports and registers, but otherwise, bit widths on wires are auto-matically inferred unless set manually by the user. The bit-width inference engine starts from the graph’s input ports and calculates node output bit widths from their respective input bit widths according to the following set of rules: inst.eecs.berkeley.edu

operation bit width

= x + y wz = max(wx, wy) + 1 = x - y wz = max(wx, wy) + 1 = x & y wz = max(wx, wy) = Mux(c, x, y) wz = max(wx, wy) = w * y wz = wx + wy = x << n wz = wx + maxNum(n) = x >> n wz = wx - minNum(n) = Cat(x, y) wz = wx + wy = Fill(n, x) wz = wx * maxNum(n) where for instance wz is the bit width of wire z, and the & rule applies to all bitwise logical op

6 Functional Abstraction

We can define functions to factor out a repeated piece of logic that we later reuse multiple times in a design. For example, we can wrap up our earlier example of a simple combinational logic block as follows: def clb(a: Bits, b: Bits, c: Bits, d: Bits): Bits = (a & b) ( ̃c & d) where clb is the function which takes a, b, c, d as arguments and re

8 Ports

Ports are used as interfaces to hardware components. A port is simply any Data object that has directions assigned to its members. Chisel provides port constructors to allow a direction to be added (input or output) to an object at con-struct time. Primitive port constructors take the number of bits as the first argument (except booleans which are

11 State Elements

The simplest form of state element supported by Chisel is a positive-edge-triggered register, which can be instantiated functionally as: Reg(in) This circuit has an output that is a copy of the input signal in delayed by one clock cycle. Note that we do not have to specify the type of Reg as it will be automatically inferred from its input when ins

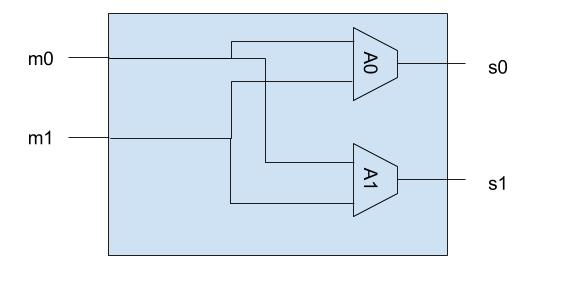

11.2 Conditional Updates

In our previous examples using registers, we simply wired their inputs to combinational logic blocks. When describing the operation of state elements, it is often useful to instead specify when updates to the registers will occur and to specify these updates spread across several separate statements. Chisel provides condi-tional update rules in the

Termination values 0 0

Figure 1: Equivalent hardware constructed for conditional updates. Each when statement adds another level of data mux and ORs the predicate into the enable chain. The compiler effectively adds the termination values to the end of the chain automatically. Figure 1 shows how each conditional update can be viewed as adding a mux to the input of a regi

12 Memories

Chisel provides facilities for creating both read only and read/write memories. inst.eecs.berkeley.edu

13 Interfaces and Bulk Connections

For more sophisticated components it is often useful to define and instantiate interface classes while defin-ing component IO. First and foremost, interface classes promote reuse allowing users to capture once and for all common interfaces in a useful form. Secondly, interfaces allow users to dramatically reduce wiring by supporting bulk connection

13.1 Port Classes, Subclasses, and Nesting

As we saw earlier, users can define their own interfaces by defining a class that subclasses Bundle. For example, a user could define a simple link for handshaking data as follows: class SimpleLink extends Bundle { val data = Bits(width=16,dir=’output); val rdy = Bool(dir=’output); } We can then extend SimpleLink by adding parity bits using bundle

13.2 Bundle Vectors

Beyond single elements, vectors of elements form richer hierarchical interfaces. For example, in order to create a crossbar with a vector of inputs, producing a vector of outputs, and selected by a UFix input, we utilize the Vec constructor: class CrossbarIo(n: Int) extends Bundle { val in = Vec(n){ new PLink().flip() }; val sel = UFix(width = (log

15 Polymorphism and Parameterization

Scala is a strongly typed language and uses parameterized types to specify generic functions and classes. In this section, we show how Chisel users can define their own reusable functions and classes using param-eterized classes. This section is advanced and can be skipped at first reading. inst.eecs.berkeley.edu

16 Acknowlegements

Many people have helped out in the design of Chisel, and we thank them for their patience, bravery, and belief in a better way. Many Berkeley EECS students in the Isis group gave weekly feedback as the de-sign evolved including but not limited to Yunsup Lee, Andrew Waterman, Scott Beamer, Chris Celio, etc. Yunsup Lee gave us feedback in response to

Chisel Introduction Intensive (Beginner Track)

How to use a Chisel CORRECTLY

How To Use a Chisel (The Correct Method)

|

Chisel 3.0 Tutorial (Beta)

12 Jan 2017 Chisel is a hardware construction language embedded in the high-level programming language. Scala. At some point we will provide a proper refer-. |

|

Chisel – Accelerating Hardware Design - Berkeley

16 Jan 2015 Chisel. 7. A hardware construction language ... Well formed Chisel graphs are synthesizable. ... online documentation and tutorial. |

|

Getting Started with Chisel

22 May 2015 structing Hardware In a Scala Embedded Language) ... where you want to place the Chisel tutorial and type:. |

|

Chisel Tutorial

19 Nov 2011 This document is a tutorial introduction to Chisel (Constructing Hardware In a Scala Embedded Language). Chisel is a hardware construction ... |

|

Chisel 2.2 Tutorial

29 Aug 2014 Chisel is a hardware construction language embedded in the high-level programming language. Scala. At some point we will provide a proper refer-. |

|

Chisel Tutorial

7 Jan 2012 Chisel is a hardware construction language embedded in the high-level programming language Scala. At some point we will provide a proper ... |

|

Digital Design in Chisel

5 Nov 2020 Chisel is not a high-level synthesis language ... Chisel is a small language. ? On purpose ... https://github.com/ucb-bar/chisel-tutorial. |

|

Getting Started with Chisel

27 Aug 2014 structing Hardware In a Scala Embedded Language) ... This is the Chisel tutorial directory structure you should see which is explained more ... |

|

White Paper - Investigate the high-level HDL Chisel

18 Oct 2013 Chisel aims to provide a language embedded in ... language tutorials of a more recent date. During the case study. Chisel 2.0 was released |

|

Digital Design with Chisel - Martin Schoeberl

This book is a tutorial in digital design and the Chisel language; it is not a Chisel language reference nor is it a book on complete chip design. |

|

Chisel - RISC-V International

16 jan 2015 · not robust and so largely manual process proprietary tools Chisel 7 A hardware construction language “synthesizable by construction” |

|

Digital Design with Chisel - 400 Bad Request - DTU

This book is a tutorial in digital de- sign and the Chisel language; it is not a Chisel language reference, nor is it a book on complete chip design All code examples |

|

Digital Design with Chisel - DTU

[12] provides a general introduction to Scala This book is a tutorial in digital de- sign and the Chisel language; it is not a Chisel language reference, nor is it a book |

|

PyMTL Tutorial - Computer Systems Laboratory - Cornell University

https://github com/cornell-brg/pymtl-tutorial-isca2019 structural, behavioral, + TB HDL Hardware Description Language RTL Sim TB Example: Chisel |

|

Digital Design in Chisel - RISC-V 協会

18 sept 2020 · Constructing Hardware In a Scala Embedded Language ▷ If it compiles, it is executed it generates hardware ▷ Chisel is a so-called embedded domain- specific language 11 / 44 https://github com/ucb-bar/chisel-tutorial |

|

Chisel Tutorial - GradeBuddy

19 nov 2011 · Chisel is a hardware construction language embedded in the high-level programming language Scala At some point we will provide a proper |

|

Open Hardware: Initial Experiences with Synthesizing - Diva Portal

well as the new open-source hardware description language Chisel A 32 bit function as an introduction and a foundation for anyone who wishes to learn |