addressing modes in computer architecture ppt

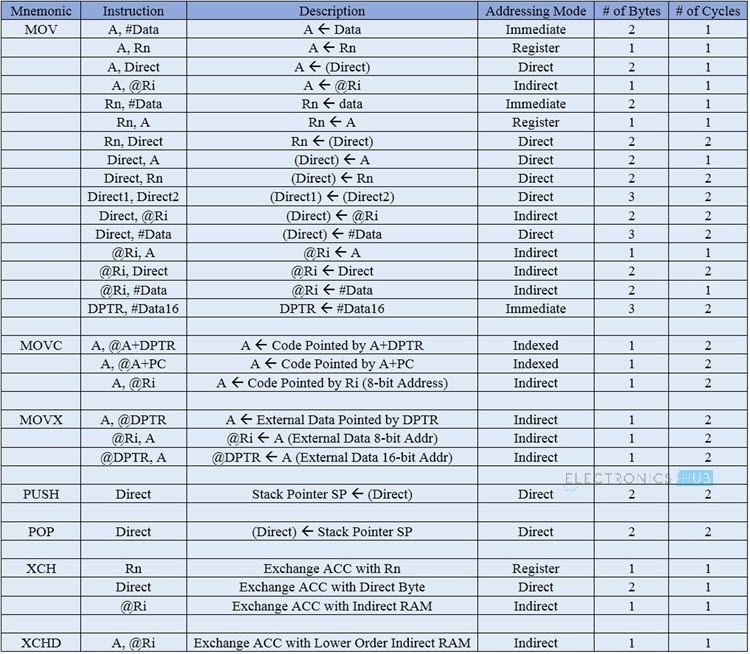

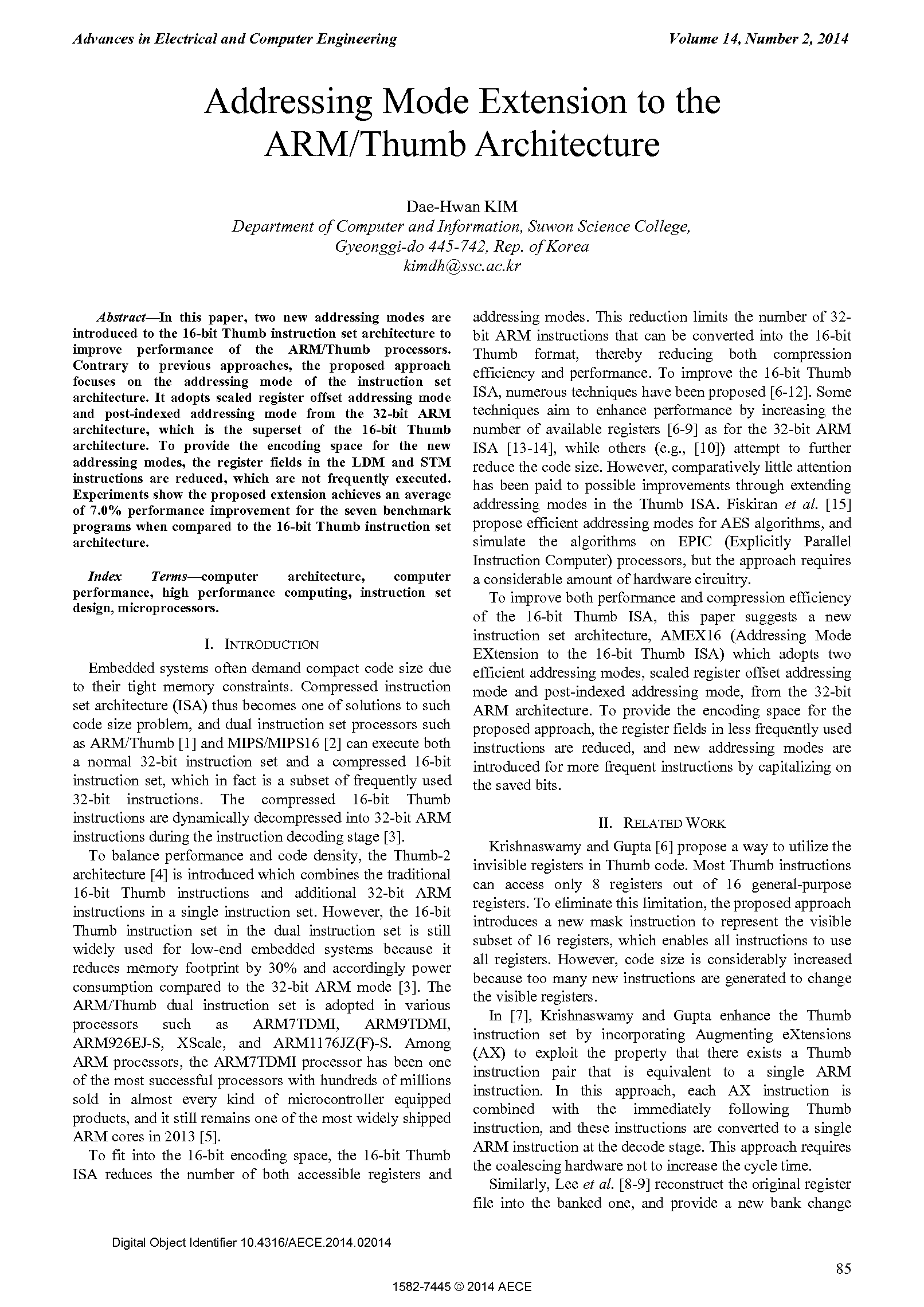

|

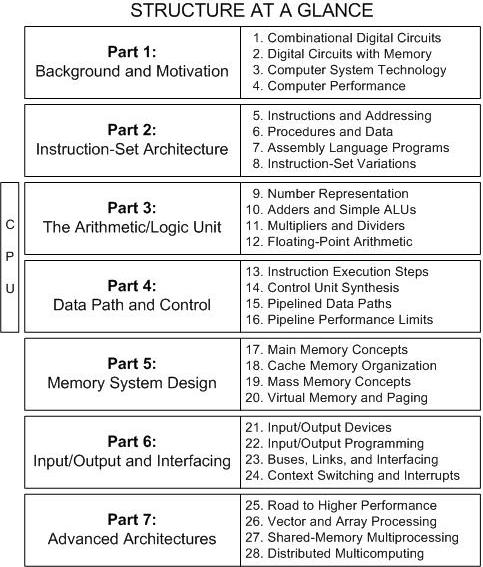

Chapter 11 Instruction Sets: Addressing Modes and Formats

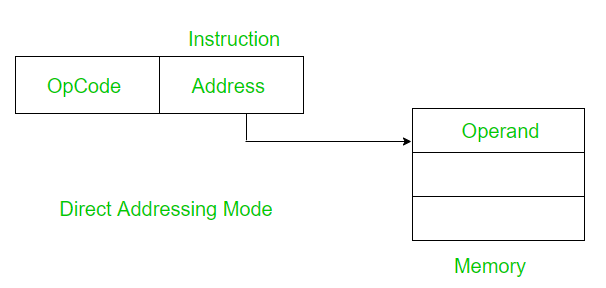

PowerPC Addressing Modes • Load/store architecture —Indirect – Instruction includes 16 bit displacement to be added to base register (may be GP register) – Can replace base register content with new address —Indirect indexed – Instruction references base register and index register (both may be GP) – EA is sum of contents |

|

CS305: Computer Architecture

Five Common Addressing Modes Base lw $t1 4($s2) lw $t1 ($s2) #indirect addressing Computer Architecture 4 op rs rt Address Register Memory ± |

|

Addressing Modes

Register addressing mode ∗ Operands are located in registers ∗ It is the most efficient addressing mode Immediate addressing mode ∗ Operand is stored as part of the instruction This mode is used mostly for constants ∗ It imposes several restrictions ∗ Efficient as the data comes with the instructions Instructions are generally prefetched Both addre |

What is the difference between EA & PC addressing mode?

EA= PC + Address field value PC= PC + Relative value. Base register addressing mode: Base register addressing mode is used to implement inter segment transfer of control.In this mode effective address is obtained by adding base register value to address field value. EA= Base register + Address field value. PC= Base register + Relative value.

What is a good addressing mode in assembly language?

The key to good assembly language programming is the proper use of memory addressing modes. The memory address of an operand consists of two components: Starting address of memory segment. Effective address or Offset: An offset is determined by adding any combination of three address elements: displacement, base and index.

What are PowerPC addressing modes?

PowerPC Addressing Modes • Load/store architecture —Indirect – Instruction includes 16 bit displacement to be added to base register (may be GP register) – Can replace base register content with new address —Indirect indexed – Instruction references base register and index register (both may be GP) – EA is sum of contents • Branch address

What are the different types of addressing modes?

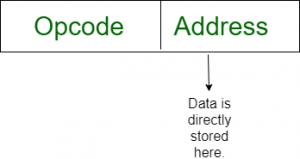

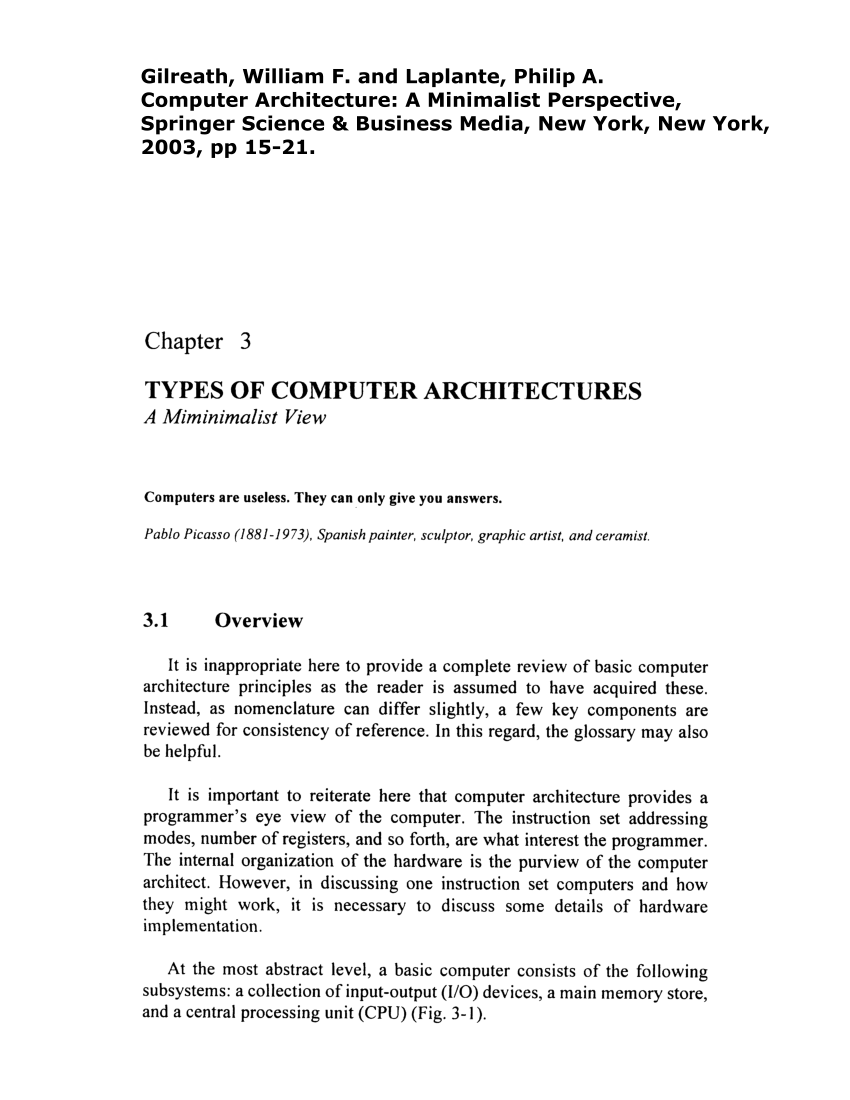

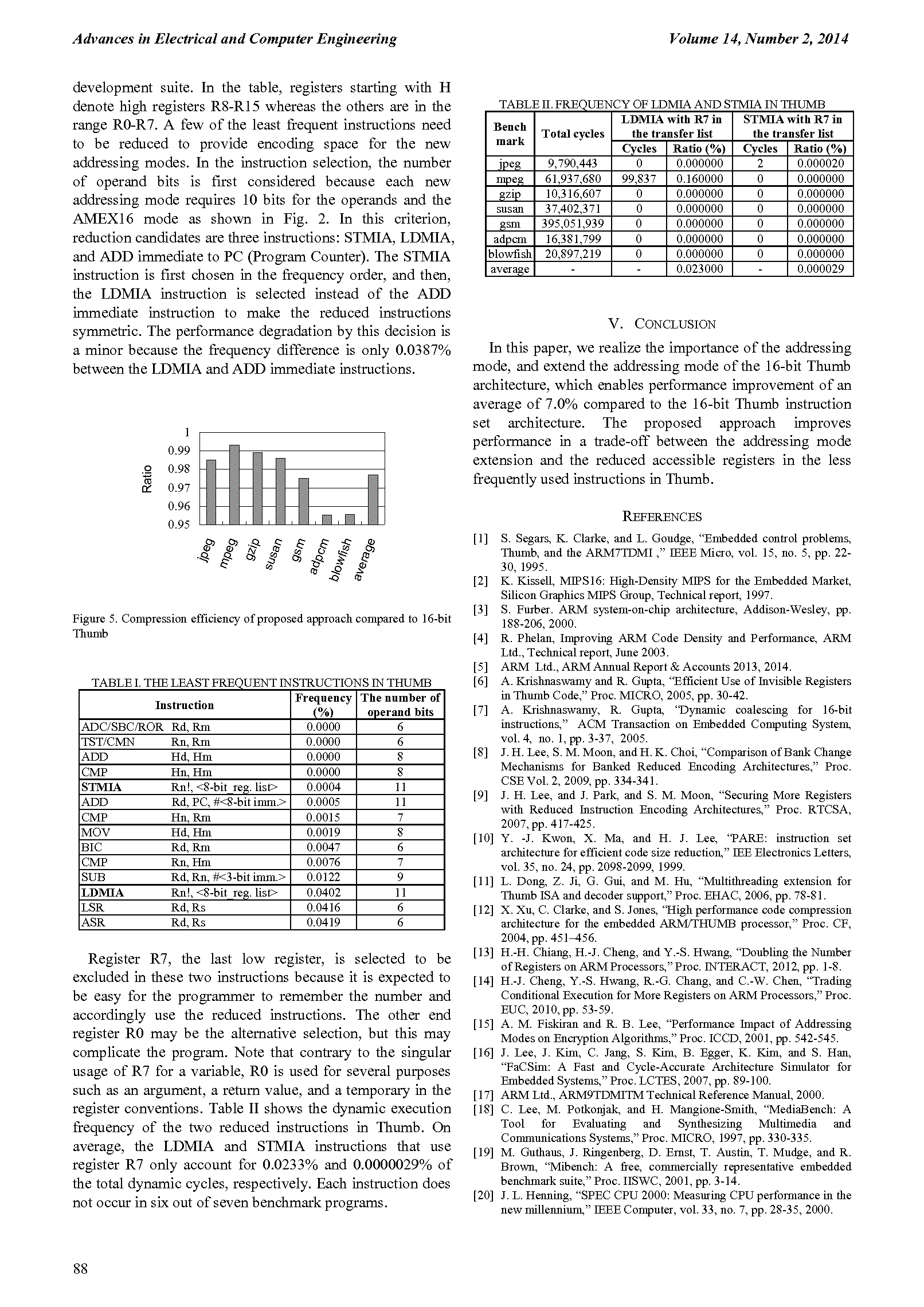

William Stallings Computer Organization and Architecture 6thEdition Chapter 11 Instruction Sets: Addressing Modes and Formats Addressing Modes • Immediate • Direct • Indirect • Register • Register Indirect • Displacement (Indexed) • Stack Immediate Addressing • Operand is part of instruction • Operand = address field • e.g. ADD 5

Simple Addressing Modes

Register addressing mode ∗ Operands are located in registers ∗ It is the most efficient addressing mode Immediate addressing mode ∗ Operand is stored as part of the instruction This mode is used mostly for constants ∗ It imposes several restrictions ∗ Efficient as the data comes with the instructions Instructions are generally prefetched Both addre

Memory Addressing Modes

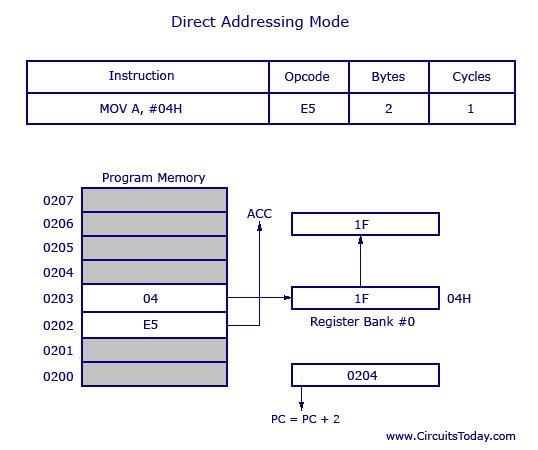

• Direct addressing mode ∗ Offset is specified as part of the instruction Assembler replaces variable names by their offset values Useful to access only simple variables service.scs.carleton.ca

add AX,table1[SI]

SI needs to hold the element offset in bytes When we use the scale factor we avoid such byte counting service.scs.carleton.ca

Based-indexed addressing with no scale factor

Effective address is computed as base + index + signed displacement Useful in accessing two-dimensional arrays Displacement → points to the beginning of the array Base and index registers point to a row and an element within that row Useful in accessing arrays of records Displacement → represents the offset of a field in a record Base and index reg

Illustrative Examples

Insertion sort ∗ ins_sort.asm ∗ Sorts an integer array using insertion sort algorithm Inserts a new number into the sorted array in its right place Binary search service.scs.carleton.ca

∗ bin_srch.asm

∗ Uses binary search to locate a data item in a sorted array » Efficient search algorithm service.scs.carleton.ca

Example 2

Two-dimensional array Finds sum of a column Uses “based-indexed addressing with scale factor” to access elements of a column service.scs.carleton.ca

3 Examples of Addressing Modes in Computer Organization & Architecture

Addressing Modes in Computer Organization & Architecture

4 Examples of Addressing Modes in Computer Organization & Architecture

|

Chapter 11 - Part 1 - PPT - Mano & Kime - 2nd Ed

Computer architecture. ? Operand addressing. • Addressing architecture. • Addressing modes. ? Elementary instructions. • Data transfer instructions. |

|

1. Instruction Formats One address. Two address. Zero address

some data stored in computer registers or memory words. The way the operands are chosen during program execution in dependent on the addressing mode of the |

|

Computer Organization and Architecture Lecture Notes

Table 2.1Basic Addressing Modes. Table 2.1 indicates the address calculation performed for each addressing mode. Different opcodes will use different addressing |

|

Chapter 11 - Part 1 - PPT - Mano & Kime - 2nd Ed

Computer architecture. ? Operand addressing. • Addressing architecture. • Addressing modes. ? Elementary instructions. • Data transfer instructions. |

|

CS8491 COMPUTER ARCHITECTURE II YEAR / 4th SEMESTER

Immediate Addressing Mode: ? MIPS immediate addressing means that one operand is a constant within the instruction itself. ? The advantage of using it is that |

|

Systems I: Computer Organization and Architecture

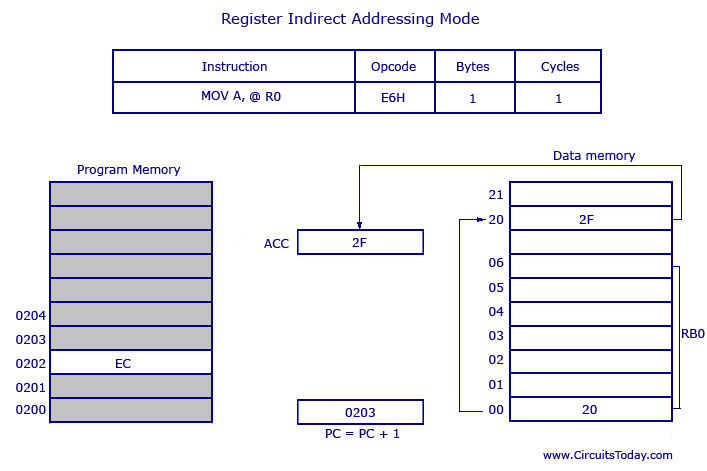

Addressing Modes. • There are four different types of operands that can appear in an instruction: – Direct operand - an operand stored in the. |

|

COMPUTER ORGANIZATION (15A05402)

sequences – Addressing modes and instructions –Simple input programming – pushdown John L.Hennessy and David A.Patterson “Computer Architecture a ... |

|

Chapter 2 IA-32 Processor Architecture

Understand how memory is addressed in protected mode and real-address mode A computer's system bus usually consists of there separate buses:. |

|

11_ Instruction Sets addressing modes .ppt [Compatibility Mode]

William Stallings. Computer Organization and Architecture. 7th Edition. Chapter 11. Instruction Sets: Addressing Modes and Formats |

|

Data Types and Addressing Modes 29

The fundamental data types of the Intel Architecture are bytes words |

|

Chapter 11 - Part 1 - PPT - Mano & Kime - 2nd Ed

ECE 3401 Lecture 21 Instruction Set Architecture Overview ▫ Computer architecture ▫ Operand addressing • Addressing architecture • Addressing modes |

|

11_ Instruction Sets addressing modes ppt [Compatibility Mode]

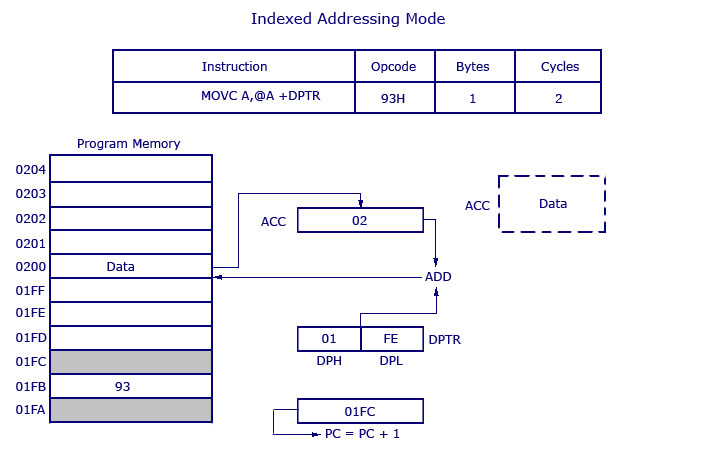

Computer Organization and Architecture Addressing Modes and Formats Direct Addressing Diagram Address A Opcode Instruction Memory Operand |

|

Addressing Modes

William Stallings Computer Organization and Architecture 8th Edition Chapter 11 Instruction Sets: Addressing Modes and Formats |

|

Chapter 11 Instruction Sets: Addressing Modes and Formats - IGNTU

Pentium and PowerPC addressing modes • Instruction formats —Look in A, find address (A) and look there for operand • ADD (A) —Memory organization |

|

1 Instruction Formats One address Two address Zero - IARE

An example of a general register type of organization was presented in Fig 7 1 Computers use addressing mode techniques for the purpose of diagram that shows the timing relationship that must exist between the control signals and the |

|

Chapter 11 Instruction Sets: Addressing Modes and Formats

Computer Organization and Architecture Instruction Set modes is a key component of instruction set design Direct Addressing in x86 architecture • Intel x86 |

|

Instruction Sets: Characteristics and Functions Addressing Modes

Addressing Modes and Formats William Stallings, Computer Organization and Architecture 6th Edition 2 What is Indirect Addressing Diagram Address A |

|

William Stallings Computer Organization and Architecture

Computer Organization and Architecture Addressing Modes and Formats 6 10 - Direct Addressing Diagram Address A Opcode Instruction Memory |

|

Addressing Modes

To be used with S Dandamudi, “Fundamentals of Computer Organization and Pentium supports three fundamental addressing modes: ∗ Register mode |

|

Addressing Modes and Formats

Computer Organization and Architecture Addressing Modes • Immediate Direct Addressing Diagram Address A Opcode Instruction Memory Operand |

![PDF]Computer Organisation and Architecture 8e by William Stallingspdf PDF]Computer Organisation and Architecture 8e by William Stallingspdf](https://ehindistudy.com/wp-content/uploads/2019/08/20190815_2205042770621668086004490-300x142.png)

![PDF] A gentle introduction to addressing modes in a first course PDF] A gentle introduction to addressing modes in a first course](https://media.geeksforgeeks.org/wp-content/uploads/vn_cpu.png)

![AMI Chapter 1 - [PDF Document] AMI Chapter 1 - [PDF Document]](https://0.academia-photos.com/attachment_thumbnails/34772911/mini_magick20190320-22861-lq2bdf.png?1553149998)