cpsr arm

What is the Cpsr in ARM?

The Linux/ARM embedded platform

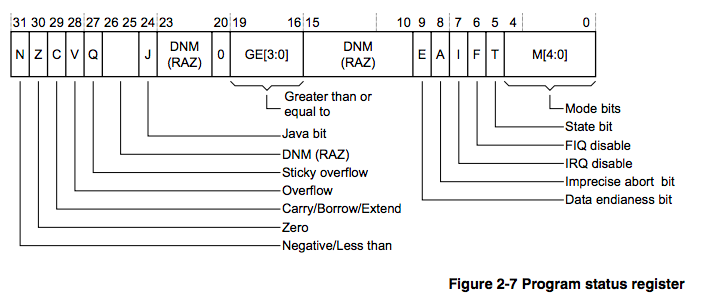

ARM v6/v7 maintains a status register called the CPSR (current program status register) that holds four status bits, negative (N), zero (Z), carry (C), and overflow (O).

These bits can be used for conditional execution of subsequent instructions.What is CPSR_c?

c = Control. x = eXtension. s = Status. f = Flags.

The purpose of using e.g.

CPSR_c is that it allows you to update only parts of the status register (in this case the control bits) without affecting the other parts.What does Cpsr stand for?

Current Program Status Register (CPSR) Core Register Access.

The Current Program Status Register (CPSR) holds processor status and control information.

MoreBy manipulating the CPSR, you can control the execution of instructions and handle different processor modes.

The SPSR, on the other hand, allows you to save and restore the processor state when handling exceptions or interrupts.

|

ARM Exceptions

ARM Exception Vector Table. ? ARM Exception Priorities asserted (LOW) and the F bit in the CPSR is clear (enable) ... CPSR[5] = 0 // ARM state. |

|

Práctica 1: Descubriendo el entorno de trabajo

Adquirir práctica en el manejo del repertorio de instrucciones ARM 1.3 Introducción a la arquitectura ARM ... Registro de Estado del ARM (CPSR). |

|

Exception and Interrupt Handling in ARM

ARM processor has 7 modes of operation. •Switching between modes can be done manually through modifying the mode bits in the CPSR register. •Most |

|

The ARM Instruction Set

The ARM Instruction Set - ARM University Program - V1.0. 8. The Program Status Registers. (CPSR and SPSRs). Copies of the ALU status flags (latched if the. |

|

Conjunto de Instrucciones ARM

Coloca bits apropiados en CPSR. Si el core implementa instrucciones ARM arquitectura 4T y está en estado Thumb entonces. Se entra al estado ARM . |

|

Disabling Interrupts at Processor Level Application Note AT91 ATM

corresponding bit in the CPSR (Current Processor Status Register): AT91 ARM Thumb ... r0 CPSR orr r0 |

|

Q1. Explain briefly the data processing instructions for ARM

A unique and powerful feature of the ARM processor is the ability to They update the cpsr flag bits according to the result but do not affect other. |

|

The ARM Instruction Set

ARM has 37 registers in total all of which are 32-bits long. • 1 dedicated program counter Specific instructions to allow access to CPSR and SPSR. |

|

The ARM Architecture

Designs the ARM range of RISC processor ARM has 37 registers all of which are 32-bits long. ... the current program status register cpsr. |

|

Chapter 6 ARM Instruction Set

But only set the values of the NZCV bits of the. CPSR register. ?. Do not need to apply to S suffix for comparison instruction to update the flags in CPSR |

|

Fundamentals of ARMv8-A

3 mar 2017 · Where the term ARM is used it means “ARM or any of its subsidiaries as In AArch64, the components of the traditional CPSR are supplied as |

|

The ARM Instruction Set

ARM has 37 registers in total, all of which are 32-bits long • 1 dedicated program Specific instructions to allow access to CPSR and SPSR * Note : When in a |

|

The ARM Architecture - Washington

Designs the ARM range of RISC processor cores ▫ Licenses ARM has 37 registers all of which are 32-bits long the current program status register, cpsr |

|

Présentation Architecture et jeu dinstructions ARM - SoC

▷ CPSR : Instructions spécifiques L'instruction MOV permet d'effectuer des transferts `a destination de registres : MOV r3 ,#4 |

|

UNIT-4 ARM PROGRAMMING MODEL

➢ If you use the S suffix on a data processing instruction, then it updates the flags in the CPSR ➢ Move and logical operations update the carry flag C, negative |

|

Exception and Interrupt Handling in ARM - IC/Unicamp

ARM processor has 7 modes of operation •Switching between modes can be done manually through modifying the mode bits in the CPSR register •Most |

|

Cours 8 Architectures & Systèmes- introduction à lARM

9 mar 2015 · ARM fourni les cœurs de processeur, les industriels peuvent y adjoindre Current Program Status Register (CPSR): registre d'état accessible |

|

1) Fixed instruction length is a feature of one of the - NPTEL

instruction branches to the initialization code a) True b) False 22) An instruction that is used to move data from an ARM Register to a Status Register (CPSR or |

![cpsr - [PDF Document] cpsr - [PDF Document]](https://imgv2-2-f.scribdassets.com/img/document/20270295/149x198/77691c3557/1260224801?v\u003d1)

![cpsr - [PDF Document] cpsr - [PDF Document]](http://pdf-html.ic37.com/pdf_file_B/20200531/pdf_img/pdf6/TI/TL7700CPSR_datasheet_1060040/TL7700CPSR_datasheet_ic_pdf_2.jpg)