TD n°6 : Gestion de la mémoire CORRECTION

TD n°6 : Gestion de la mémoire CORRECTION

Dans un segment de longueur 200 les déplacements valides sont dans l'intervalle [0-199]. Exercice 3 – Pagination. 1) L'espace d'adressage du processus est l

Travaux Dirigés

Travaux Dirigés

15 déc. 2016 Une segmentation et une pagination ? • partitionnement de l'espace d'adressage logique/physique ;. • La segmentation considère la mémoire comme ...

Gestion de la mémoire Exercice 1 :

Gestion de la mémoire Exercice 1 :

- Utilisation combinée des techniques de pagination et de segmentation : l'espace d'adressage virtuel d'un processus est composé de segments contigus. Chaque

Exercice 1 – Systèmes de nombres Exercice 2 – Mémoire contiguë

Exercice 1 – Systèmes de nombres Exercice 2 – Mémoire contiguë

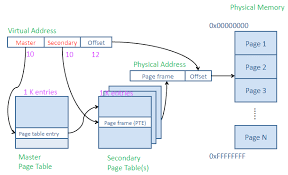

Expliquez. Exercice 4 – Pagination à 2 niveaux. On considère un système de gestion de mémoire paginée à deux niveaux tel que : — Les adresses virtuelles et

Systèmes dexploitation & Programmation concurrente TD Gestion

Systèmes dexploitation & Programmation concurrente TD Gestion

Exercice 1: Ordonnancement et gestion mémoire (exam. 1-2017). Soit une On considère un système de gestion de mémoire virtuelle à un seul niveau de pagination.

Questions a) Rappeler brièvement le principe du swapping de la

Questions a) Rappeler brièvement le principe du swapping de la

TD N° 03 Gestion de mémoire. Enseignant : KHARROUBI S. 2. Exercice 02. Soi un système de pagination dont la taille de page est de 1KO la mémoire usager est de

Pagination de la mémoire

Pagination de la mémoire

Exercice 2 : En supposant la table des pages suivante : Question 1 : un bloc est de 1 kilo-‐octet. Donc il faut les déplacements dans une page sont codés

Questions de cours : Exercice 1:

Questions de cours : Exercice 1:

Un système multiprogrammé gère le partage des ressources (mémoire processeur

TD Architecture des ordinateurs.pdf

TD Architecture des ordinateurs.pdf

$E000. Page 13. Exercice 3 : adressage de mémoire. La capacité des programme est exécuté dans un système qui utilise la pagination de la mémoire dont la ...

Gestion de la mémoire Exercice 1 :

Gestion de la mémoire Exercice 1 :

- Utilisation combinée des techniques de pagination et de segmentation : l'espace d'adressage virtuel d'un processus est composé de segments contigus. Chaque

Pagination de la mémoire

Pagination de la mémoire

Exercice 2 : En supposant la table des pages suivante : Question 1 : un bloc est de 1 kilo-?octet. Donc il faut les déplacements dans une page sont.

Travaux Dirigés

Travaux Dirigés

15 déc. 2016 Correction exercice I ... Exercice III: algorithme LRU dans le pire cas ... Dans un système de gestion mémoire virtuelle à pagination.

Untitled

Untitled

Exercice III. On donne ci-dessous un extrait de la table des segments d'un processus : N° du segment Taille du segment Position en mémoire. 30KO. 16Ko. 32Ko.

Exercice 1 – Systèmes de nombres Exercice 2 – Mémoire contiguë

Exercice 1 – Systèmes de nombres Exercice 2 – Mémoire contiguë

Semaine 5 – Mémoire contiguë et pagination. Remarque : Cette séance est une séance de TD. Exercice 1 – Systèmes de nombres. 1. Du binaire à l'hexadécimal

EXERCICES DIRIGES 6 Gestion de la mémoire centrale Exercice 1

EXERCICES DIRIGES 6 Gestion de la mémoire centrale Exercice 1

Exercice 1 : Gestion d'une mémoire par zones Décrivez le principe de la pagination appliquée à la segmentation de la mémoire. Comment s'effectue.

Chapitre 7 : Gestion de la mémoire

Chapitre 7 : Gestion de la mémoire

Les principales stratégies de gestion de la mémoire se classent en trois Solution de l'exercice 1 ... Stratégies de remplacement en pagination.

Gestion de la mémoire

Gestion de la mémoire

Exercice 1. Pagination `a la demande. Exercice 4. ... La mémoire virtuelle est implémentée avec la pagination et la taille de la page.

8 – PAGINATION MÉMOIRE

8 – PAGINATION MÉMOIRE

TD 8 Mémoire Trap (p) : Défaut de page pour la page p Charg (pc) : Chargement de la page p dans la case c en mémoire centrale Dech (pc) : Déchargement de la page p se trouvant à la place c en mémoire centrale

TD n°6 : Gestion de la mémoire CORRECTION

TD n°6 : Gestion de la mémoire CORRECTION

Exercice 6 – Temps d'accès 1) a) Dans l’algorithme LRU on retire la page la moins récemment utilisée Il s’agit donc de choisir une page selon le critère de la colonne Tdernier accès La page à retirer est celle chargée dans le cadre 1 qui a été accédée au temps 255

Searches related to exercice pagination mémoire PDF

Searches related to exercice pagination mémoire PDF

Exercice 3 – Pagination Dans un système paginé les pages font 256 mots mémoire et on autorise chaque processus à utiliser au plus 4 cadres de la mémoire centrale On considère la table des pages suivante du processus P1 : Page 0 1 2 3 4 5 6 7 Cadre '011 '001 '000 '010 '100 '111 '101 '110 Présence oui non oui non non non oui non

Comment fonctionne la pagination à la demande ?

Un système qui implémente la pagination à la demande dispose de 4 cadres de mémoire physique qui sont toutes occupées, à un instant donné, avec des pages de mémoire virtuelle. Le tableau ci-dessous donne, pour chaque cadre de mémoire, le moment du chargement de la pagequ’elle contient (Tchargement), le temps du dernier accès à cette page (Tdernier

Quels sont les segments de la mémoire?

La mémoire est composée de cases (cadres ou frames) de taille 4 KO. L’espace logique d’un processus est composé de trois segments (le segment de code, le segment de données et le segment de pile). Chaque segment est composé d’une ou plusieurs pages.

Comment calculer la numérotation des pages d’un segment?

La numérotation des pages d’un segment est relative au segment. - Utilisation de l’algorithme de remplacement de pages LRU (i.e. la moins récemment utilisée). 1) Calculez le format d’une adresse virtuelle et le format d’une adresse physique (i.e. réelle), en spécifiant le nombre de bits réservés pour chaque champ.

Comment choisir un système de gestion de mémoire?

Considérez un système de gestion de mémoire qui a les caractéristiques suivantes : ? Un adressage virtuel sur 32 bits ? Une taille de Page de 4Ko ? Une mémoire physique de 1 Mo a) Supposez que le système utilise la segmentation paginée et que l’adresse virtuelle est de la forme :

TD 8 Mémoire8 - PAGINATION M

ÉMOIRE

1.PAGINATION

Le principe de la pagination r

éside dans la division de la mémoire en zones de tailles fixes appel ées "pages". L'espace de travail d'un processus est divisé en pages. Quand le processus est exécuté, seules les pages dont il a besoin sont chargées en mémoire centrale.On dispose d'une machine monoprocesseur, ayant une m

émoire centrale de 32K mots, une

page faisant 512 mots (64 pages en m émoire centrale), un bloc (unité de stockage sur le disque) faisant 512 mots. On consid ère le programme suivant :AdresseInstructionSignificationELoadx Nreg d'index X = N

Load S,Xreg accumulateur A = S[X]

Add VA = A + V

Store T,XT[X] = A

Subx KX = X K

Brxpz E + 1Si X >= 0 alors aller en E + 1

Stop Où:•X est un registre d'index,

•A est un registre accumulateur, •E est l'adresse du d ébut du programme : 512 * 1 + 508, •S et T sont des tableaux de taille [0 .. N], S [0]étant à l'adresse 512 * 11 + 168 et T[0]

se trouvant à l'adresse 512 * 12 +456, •N est une constante égale à 799 se trouvant à l'adresse 512 * 6 + 500, •V est une constante égale à 2 se trouvant à l'adresse 512 * 8 + 100, •K est une constante égale à 2 se trouvant à l'adresse 512 * 8 + 10. Ce programme effectue la chose suivante : x = N; do {T[X] = S[X] + V;

x -= K; } while (x >= 0);En fin d'ex

écution, les pages modifiées sont recopiées en mémoire secondaire.1.1. Sachant que chaque instruction, constante ou variable simple occupe un mot mémoire,

repr ésenter l'espace d'adressage du processus (numéro de page / déplacement dans la page de chaque donnée). Quels droits doiton affecter aux différentes pages du processus ?Les actions de gestion de la m

émoire peuvent être représentées à l'aide des opérations suivantes :TD 8 MémoireTrap (p) : D

éfaut de page pour la page p.Charg (p,c) :Chargement de la page p dans la case c en mémoire centrale.Dech (p,c) : D

échargement de la page p se trouvant à la place c en mémoire centrale.Mod (p,c,d) : Modification de la table des pages, p : num

éro de page du processus, c

place en m émoire centrale, d droits d'accès de la page.Le processus pr écédent dispose pour s'exécuter des pages de mémoire centrale 17, 21, 22,23, 37 et 42.

1.2.En utilisant un algorithme premier charg

é/premier déchargé et en supposant qu'au départ, aucune page n'est charg ée, décrire les actions de gestion de mémoire sous la forme d'une suite compos ée des opérations précédentes. Donner la table des pages finale.2.SEGMENTATION PAGINÉEOn consid

ère une mémoire segmentée paginée. La taille des pages est de 512 mots.Le processus P poss

ède 3 segments : le segment 0 pour le code, le segment 1 pour la pile et le segment 2 pour les donn ées. Le segment 0 a 1500 mots, le segment 1 en a 2000 et le segment 2 en a 3000. On suppose que la table des segments et les tables de pages sont déjà

chargées en mémoire.2.1.

Quels sont les droits associ

és à chaque segment ? Quel est l'avantage de découper ainsi l'espace d'adressage du processus ?Seules les pages suivantes ont

été chargées (on donne le doubletDans quelle case m

émoire est chargée la page <0, 0> ?

2.3. D écrire brièvement ce qui se passe sur une tentative de lecture en <0 : 1678>, <1 : 567> et <2 : 1600> (Ces adresses sont au format segmenté).2.4.

Conna îton l'adresse physique de la variable d'adresse virtuelle <1 : 1060> ? Si oui, quelle estelle ? Sinon, justifiez.3. CACHE ET M

ÉMOIRE VIRTUELLE

Avec une m

émoire paginée, l'accès à une donnée nécessite deux accès à la mémoire : un

pour lire la table des pages, l'autre pour lire la donnée. Pour ne pas diviser par deux les

performances du syst ème, on utilise un cache spécial, appelé TLB (Translation Lookaside TD 8 MémoireBuffers), qui permet de stocker le coupleées. 3.1.

On suppose qu'un acc

ès à la TLB demande 20 ns et qu'un accès mémoire demande 100 ns. Pour une TLB avec un taux de hit de 90%, quel est le temps moyen d'accès à une donnée ?

En plus de la TLB qui permet une translation rapide de l'adresse logiqueà l'adresse

physique, le syst ème dispose d'un cache pour améliorer la vitesse d'accès aux données. Le cache est une m émoire à accès rapide, structurée en lignes. Chaque ligne stocke un bloc de donn ées d'une part, tout ou partie de l'adresse du bloc permettant d'identifier le bloc de façon unique, ainsi que diverses informations relatives à la validité, l'ancienneté, ... dudit

bloc.La combinaison de la m

émoire cache et de la mémoire virtuelle est délicate : ou bien le cache contient les adresses physiques des blocs, et dans ces conditions la traduction adresse virtuelle adresse physique doit être faite entre le processeur et le cache; ou bien le cache contient les adresses virtuelles des blocs, et la traduction adresse virtuelleadresse physique a lieu entre le cache et la mémoire.3.2.

Repr ésentez schématiquement l'organisation de la hiérarchie mémoire dans les deux cas.Quels sont les avantages et inconv

énients de chaque organisation ?

quotesdbs_dbs5.pdfusesText_10[PDF] difference entre pagination et segmentation

[PDF] conversion adresse logique adresse physique

[PDF] pagination et segmentation pdf

[PDF] pagination systeme d'exploitation

[PDF] telecharger un livre de grammaire pdf

[PDF] larousse conjugaison pdf

[PDF] telecharger larousse difficultés grammaticales pdf

[PDF] larousse grammaire francais

[PDF] larousse orthographe pdf

[PDF] larousse livre de bord orthographe pdf

[PDF] introduction grammaire generative

[PDF] chomsky théorie

[PDF] chomsky linguistique pdf

[PDF] aspects de la théorie syntaxique pdf