Exercices de Révision sur les Circuits Combinatoires Multiplexeur

Exercices de Révision sur les Circuits Combinatoires Multiplexeur

Exercices de Révision sur les Circuits. Combinatoires Multiplexeur

Corrigé de lexamen final_TS412

Corrigé de lexamen final_TS412

Exercice 01 (04 5 pts). A. Réaliser les fonctions booléennes suivantes à l'aide d multiplexeur ne suffit pas à lui seul pour générer la fonction F4. Une ...

Université des Sciences et de la Technologie dOran Faculté des

Université des Sciences et de la Technologie dOran Faculté des

Figure 15: Circuit logique d'un multiplexeur 4 vers 1. 3.10 Le démultiplexeur. Le démultiplexeur est un circuit combinatoire à une seule entrée (E) et N sorties

Exercice 1: Utilisation dun multiplexeur

Exercice 1: Utilisation dun multiplexeur

Exercice 1: Utilisation d'un multiplexeur Implanter la fonction représentée par la table de Karnaugh ci-dessous en utilisant un démultiplexeur de 4 bits.

ELECTRONIQUE NUMERIQUE Logique combinatoire et multiplexage

ELECTRONIQUE NUMERIQUE Logique combinatoire et multiplexage

16- Exercice 16 : (Multiplexeur). Dessiner le schéma interne d'un multiplexeur à 3 Exercice 7- Multiplexeurs/démultiplexeurs. 1-Réponse : L'équation de la ...

TD systèmes logiques.pdf

TD systèmes logiques.pdf

(Codeurs Décodeurs

Exercices de logique combinatoire : Multiplexeur Démultiplexeur

Exercices de logique combinatoire : Multiplexeur Démultiplexeur

Exercices logique combinatoire Mux_Démux- V0.1. 1/2. Lycée Jules Ferry – Versailles - LD. 2007 - 2008. Exercices de logique combinatoire : Multiplexeur

ELA114 : conception numérique en VHDL

ELA114 : conception numérique en VHDL

2.2.4 Le multiplexeur. Le multiplexeur est la fonction inverse du démultiplexeur. C'est un sélecteur de données ou aiguillage convergent. Il peut transformer

RESUME DE COURS ET CAHIER DEXERCICES

RESUME DE COURS ET CAHIER DEXERCICES

4) Réaliser la même fonction S que dans l'exercice 2) a) avec un multiplexeur 4 vers 1 et un simple inverseur en plus. 5) Décodeur/Démultiplexeur. Un décodeur

Disponible sur http://www.esinsa.unice.fr/~fmuller/

Disponible sur http://www.esinsa.unice.fr/~fmuller/

3 - Multiplexeurs - Démultiplexeurs Le compte-rendu doit comporter pour chaque exercice: • une partie théorique. • un ou des schémas avec des symboles ...

Exercices de Révision sur les Circuits Combinatoires Multiplexeur

Exercices de Révision sur les Circuits Combinatoires Multiplexeur

Combinatoires Multiplexeur

Corrigé de lexamen final_TS412

Corrigé de lexamen final_TS412

Corrigé de l'examen final Exercice 01 (04 5 pts) ... B. En utilisant un multiplexeur 8 vers 1 et des portes logiques

Logique combinatoire et multiplexage

Logique combinatoire et multiplexage

1- Exercice 1 : (Centrale). La fonction Multiplexeur 2 vers 1 dont le symbole logique est représenté Figure 1 Exercice 7- Multiplexeurs/démultiplexeurs.

Exercices de logique combinatoire : Multiplexeur Démultiplexeur

Exercices de logique combinatoire : Multiplexeur Démultiplexeur

Exercices de logique combinatoire : Multiplexeur Démultiplexeur. EXERCICE 1.: Soit le circuit logique suivant : E0 et E1 sont des entrées de données.

Multiplexeurs et Dmultiplexeurs

Multiplexeurs et Dmultiplexeurs

schéma ci-dessous donne une image d'un multiplexeur 4 voies (E3 à E0) Le démultiplexeur est de ce fait souvent assimilé à un décodeur binaire décimal.

Algèbre de Boole

Algèbre de Boole

Exercice. Trouver la forme simplifiée des fonctions à partir des deux tableaux ? Exercice 2 : Donner l'équation de F ? ... Multiplexeur / démultiplexeur.

VHDL - Logique programmable

VHDL - Logique programmable

Multiplexeur 4 vers 1 liste de conditions non exhaustive

TD systèmes logiques.pdf

TD systèmes logiques.pdf

1) Ecrire les nombres précédents de l'exercice 3 en base 2 . (Codeurs Décodeurs

TP N° 5 : Simulations de composants passifs: coupleurs

TP N° 5 : Simulations de composants passifs: coupleurs

Exercice 1 : Coupleurs : Exercice 2 : Multiplexeurs/demultiplexeurs : ... b) Modifier la bande passante du multiplexeur et démultiplexeur pour obtenir ...

Chapitre 6

Chapitre 6

Circuit logique de conversion et de sélection de données. ? Décodeur. ? Transcodeur. ? Codeur. ? Multiplexeur. ? Démultiplexeur. • Arithmétique binaire.

Université Abou Bekr Belkaid de Tlemcen

Faculté de Technologie

Département de Télécommunications

Corrigé de l'examen final

Niveau : L2-TTL

Matière : TS412

Date : mardi, le 15 mai 2018

Durée : 1H30min

1Exercice 01 (04, 5 pts)

A. Réaliser les fonctions booléennes suivantes à l"aide d"un décodeur 74138 (3 vers 8) et

des portes logiques : =; =;Solution

En appelant Y

i les sorties de rang i du décodeur et en affectant respectivement les poids 20, 21 et 22 à ABC, on obtient :

B. En utilisant un multiplexeur 8 vers 1 et des portes logiques, réaliser la fonction logique suivante : =+ + + + +Solution

Le nombre de variables est égal à 4, une de plus que les entrées d"adresses, le multiplexeur ne

suffit pas à lui seul pour générer la fonction F4. Une solution consiste à mettre trois variables

sur les entrées d"adresses (ABC) et la quatrième à la place des entrées de données. =̅̅+

D"où le schéma correspondant :

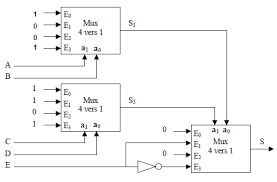

2 C. Donner l"équation logique de la fonction S du montage suivant :Solution

D'où

Exercice 02 (03 pts)

Pour afficher le résultat de la comparaison de deux nombres binaires de quatre bits A et B, on utilise un afficheur 7 segments et un comparateur. Donner la table de transcodage permettant d"afficher les segments pour écrire :S si A

> B , E si A = B, I si A < BSolution

3A>B A=B A S 1 0 0 1 0 1 1 0 1 1

E 0 1 0 1 0 0 1 1 1 1

I 0 0 1 0 1 1 0 0 0 0

Autres combinaisons x x x x x x x

Exercice 03 (07 pts)

On désire réaliser un multiplieur de deux mots binaires de deux bits selon les spécifications

suivantes : - Entrées : X = X1X0 et Y = Y1Y0 - Sortie Z : Z = X.Y où Z = Z3Z2Z1Z0,1. Etablir la table de vérité de ce multiplieur.

2. Simplifier les expressions booléennes de chacune des sorties Z

0, Z1, Z2 et Z3

3. Réaliser le logigramme du circuit complet.

4. Calculer le coût de la forme disjonctive optimale de la fonction logique Z

3.Solution

1. La table de vérité du multiplieur pour deux mots de deux bits

X.Y = Z X

X1 X0 Y

Y1 Y0 Z

Z3 Z2 Z1 Z0

0.0 = 0 0 0 0 0 0 0 0 0

0.1 = 0 0 0 0 1 0 0 0 0

0.2 = 0 0 0 1 0 0 0 0 0

0.3 = 0 0 0 1 1 0 0 0 0

1.0 = 0 0 1 0 0 0 0 0 0

1.1 = 1 0 1 0 1 0 0 0 1

1.2 = 2 0 1 1 0 0 0 1 0

1.3 = 3 0 1 1 1 0 0 1 1

2.0 = 0 1 0 0 0 0 0 0 0

2.1 = 2 1 0 0 1 0 0 1 0

2.2 = 4 1 0 1 0 0 1 0 0

2.3 = 6 1 0 1 1 0 1 1 0

3.0 = 0 1 1 0 0 0 0 0 0

3.1 = 3 1 1 0 1 0 0 1 1

3.2 = 6 1 1 1 0 0 1 1 0

3.3 = 9 1 1 1 1 1 0 0 1

42. En se référant de la table de vérité ci-dessus, on obtient les équations logiques

simplifiées à partir des diagrammes de Karnaugh des sorties comme suit : X1X0 Y1Y000 01 11 10

0001 1 1

11 1 1

10Z0 = X0Y0

X1X0 Y1Y000 01 11 10

0001 1 1

11 1 1

10 1 1

X1X0 Y1Y000 01 11 10

00 0111 1

10 1 1

X1X0 Y1Y000 01 11 10

00 0111 1

10 53. Le circuit logique d"un multiplieur deux bits :

4. Le coût de Z

3 = (4+2) = 6

Exercice 04 (05,5 pts)

1. Réaliser un diviseur de fréquence par 2 (autrement dit une bascule T) avec une bascule

D.Solution

Il suffit e reboucler la sortie inversée sur l"entrée.2. Réaliser le circuit logique et le chronogramme d"un compteur binaire modulo 10

asynchrone. Les sorties sont codé en binaire pur et les bascules utilisées sont des bascules JK sensibles aux fronts descendants. 6Solution

Le circuit logique

Le chronogramme

Le compteur est remis à zéro dès la dixième impulsion3. On considère le montage de la figure ci-dessous réalisé avec une bascule D synchrone

active sur les fronts montants du signal d"horloge.4.1 Donner les expressions des sorties A et B.

Solution

Directement à partir du schéma on lit : = + ! et = + ! 74.2 Tracer les chronogrammes de A, de B et de Q, Q est égal = 1 à t = 0

Solution

quotesdbs_dbs10.pdfusesText_16[PDF] munich to mumbai lufthansa flight status

[PDF] municipales paris 2020 sondages

[PDF] musculoskeletal system

[PDF] museum of the city of paris

[PDF] music festival expenses

[PDF] music festival marketing campaigns

[PDF] music festival target market

[PDF] music fun let's learn about notes answer key

[PDF] music tech guide to fl studio

[PDF] music worksheets pdf

[PDF] musical equations quiz 22 answers

[PDF] musical theater resume no experience

[PDF] musique film paris brule t il

[PDF] mv 44