II. Réalisation des fonctions logiques à partir de transistors.

II. Réalisation des fonctions logiques à partir de transistors.

II.1. Structure de l'inverseur logique NMOS. Le circuit est constitué de deux transistors MOS à canal N. Le transistor T1 est appelé.

Introduction aux circuits logiques de base

Introduction aux circuits logiques de base

Toute fonction logique peut être réalisée à l'aide des portes. • Réalisation d'une fonction booléenne. – Écrire l'équation de la fonction à partir de sa.

Introduction aux circuits logiques de base

Introduction aux circuits logiques de base

Toute fonction logique peut être réalisée à l'aide des portes. • Réalisation d'une fonction booléenne. – Écrire l'équation de la fonction à partir de sa.

CMOS et portes logiques

CMOS et portes logiques

Figure 1: Modèles « interrupteurs » des transistors MOS. 2 REALISATION DES PORTES LOGIQUES. 2.1 L'inverseur CMOS statique. La logique CMOS utilise les deux

GELE5340 - Chapitre 5

GELE5340 - Chapitre 5

Le nombre de transistors nécessaire pour réaliser une fonction logique est 2No`u N est le nombre d'entrées. Exemple 1. On va faire le design d'une porte NAND `

Chapitre5_IFT1215.ps (mpage)

Chapitre5_IFT1215.ps (mpage)

Ces circuits sont fait à partir de circuits logiques dont le but est d'exécuter des opérations 1? Réaliser le tableau de vérité de la fonction logique.

Composants logiques et opérateurs matériels

Composants logiques et opérateurs matériels

Les bascules réalisées à partir des portes logiques élémentaires

Conception de circuits combinatoires Les différentes approches

Conception de circuits combinatoires Les différentes approches

Technologie CMOS et réalisation des fonctions logiques. – Portes de base Comme l'un est en transistors P et l'autre en transistors N les.

Introduction générale

Introduction générale

Partie I) Fonctions logiques de base et circuits associés . Partie II) Logique combinatoire . ... d) Réalisation de fonctions logiques élémentaires.

Chapitre 1 : La diode à jonction

Chapitre 1 : La diode à jonction

2- Transistor à effet de champ à Grille isolée (MOS.FET) Chapitre 7 : Fonction commutation ... 4- Exemples de réalisation de fonctions logiques.

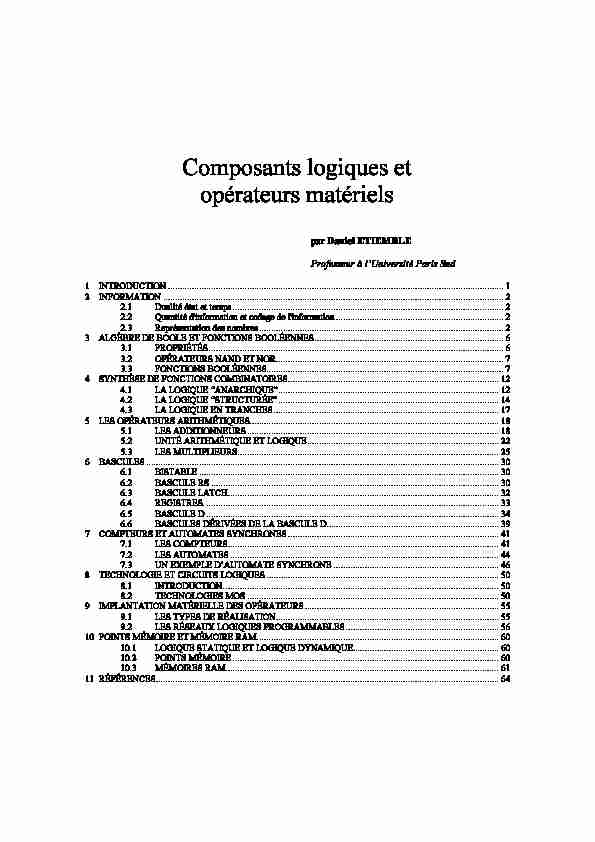

Composants logiques et

opérateurs matériels par Daniel ETIEMBLEProfesseur à lUniversité Paris Sud

1 INTRODUCTION ............................................................................................................................................1

2 INFORMATION ..............................................................................................................................................2

2.1 Dualité état et temps.................................................................................................................2

2.2 Quantité d'information et codage de l'information......................................................................2

2.3 Représentation des nombres......................................................................................................2

3 ALGÈBRE DE BOOLE ET FONCTIONS BOOLÉENNES...............................................................................6

3.1 PROPRIÉTÉS...........................................................................................................................6

3.2 OPÉRATEURS NAND ET NOR...............................................................................................7

3.3 FONCTIONS BOOLÉENNES...................................................................................................7

4 SYNTHÈSE DE FONCTIONS COMBINATOIRES........................................................................................ 12

4.1 LA LOGIQUE ANARCHIQUE............................................................................................ 12

4.2 LA LOGIQUE STRUCTURÉE............................................................................................ 14

4.3 LA LOGIQUE EN TRANCHES.............................................................................................. 17

5 LES OPÉRATEURS ARITHMÉTIQUES........................................................................................................ 18

5.1 LES ADDITIONNEURS......................................................................................................... 18

5.2 UNITÉ ARITHMÉTIQUE ET LOGIQUE................................................................................ 22

5.3 LES MULTIPLIEURS............................................................................................................. 25

6 BASCULES ................................................................................................................................................... 30

6.1 BISTABLE ............................................................................................................................. 30

6.2 BASCULE RS ........................................................................................................................ 30

6.3 BASCULE LATCH................................................................................................................. 32

6.4 REGISTRES........................................................................................................................... 33

6.5 BASCULE D .......................................................................................................................... 34

6.6 BASCULES DÉRIVÉES DE LA BASCULE D........................................................................ 39 7 COMPTEURS ET AUTOMATES SYNCHRONES........................................................................................ 41

7.1 LES COMPTEURS................................................................................................................. 41

7.2 LES AUTOMATES ................................................................................................................ 44

7.3 UN EXEMPLE DAUTOMATE SYNCHRONE ..................................................................... 46

8 TECHNOLOGIE ET CIRCUITS LOGIQUES................................................................................................. 50

8.1 INTRODUCTION...................................................................................................................50

8.2 TECHNOLOGIES MOS ......................................................................................................... 50

9 IMPLANTATION MATÉRIELLE DES OPÉRATEURS................................................................................. 55

9.1 LES TYPES DE RÉALISATION............................................................................................. 55

9.2 LES RÉSEAUX LOGIQUES PROGRAMMABLES................................................................ 56

10 POINTS MÉMOIRE ET MÉMOIRE RAM..................................................................................................... 60

10.1 LOGIQUE STATIQUE ET LOGIQUE DYNAMIQUE............................................................. 60

10.2 POINTS MÉMOIRE............................................................................................................... 60

10.3 MÉMOIRES RAM.................................................................................................................. 61

11 RÉFÉRENCES............................................................................................................................................... 64

1 Janvier 2004 1

INTRODUCTION

Le cours Composants logiques et opérateurs matériels présente les différents opérateurs de calcul et de

mémorisation que lon trouve dans les systèmes électroniques complexes, et notamment dans les

ordinateurs. La caractéristique essentielle de ces opérateurs est de travailler sur des données quantifiées

(numériques ou digitales) nutilisant que les valeurs 0 ou 1, par opposition aux circuits et opérateurs

analogiques qui travaillent sur des données continues.Les éléments dalgèbre de Boole que nous présentons constituent les fondements mathématiques

nécessaires au traitement des informations quantifiées, et à la réalisation des différents opérateurs

matériels qui réalisent ce traitement. Les portes logiques (composants logiques de base) sont associées

aux différents opérateurs de lalgèbre de Boole. Les méthodes de synthèse de fonctions combinatoires

permettent de réaliser des opérateurs de traitement plus complexes, comme les décodeurs, les

multiplexeurs, les additionneurs, les unités arithmétiques et logiques, les multiplieurs... à partir des

opérateurs matériels fondamentaux, qui vont des portes logiques aux opérateurs universels comme les

ROM, les réseaux logiques programmables (PLA, PAL...).Les bascules, réalisées à partir des portes logiques élémentaires, sont les éléments fondamentaux

permettant de mémoriser et de modifier linformation. Ils permettent de constituer les registres dune

part, et de réaliser les automates nécessaire au contrôle des processeurs et dun grand nombre de

structures matérielles. Les compteurs ne sont quun cas particulier de ces automates.La connaissance des techniques de réalisation des mémoires à accès aléatoire (RAM) permet de

comprendre certaines caractéristiques, notamment les temps daccès et la capacité de mémorisation. Les

mémoires statiques utilisent un principe de mémorisation logique, identique à celui des bascules

utilisées pour les registres. Les mémoires dynamiques utilisent un principe de mémorisation fondé sur

des principes électriques (charge et décharge de condensateurs), qui nécessitent moins de place pour

stocker chaque bit, mais impliquent un rafraîchissement périodique de linformation et un temps de

cycle au moins double du temps daccès.Si les circuits logiques ne connaissent que les valeurs 0 et 1, ils sont néanmoins implantés avec des

circuits électroniques utilisant des courants et des tensions qui sont des grandeurs continues. Le

paragraphe technologie et circuits logiques montre comment les composants logiques sont implantésavec des transistors MOS. Si le fonctionnement de ces transistors est nest que grossièrement modélisé

sous forme dinterrupteurs, la présentation permet cependant au lecteur de faire la transition entre le

monde logique des 0 et des 1, et le monde de la technologie des circuits intégrés. Nous soulignons

limportance croissante des réseaux logiques programmables, qui offrent une technique rapide et

relativement peu coûteuse de réalisation de circuits intégrés à côté des méthodes plus traditionnelles

(optimisés à la demande).Les techniques présentées dans ce chapitre ont pour but de permettre au lecteur de concevoir des

opérateurs matériels dune part, et de comprendre pour les utiliser au mieux les logiciels de CAO pour

la conception logique qui sont associées maintenant à toutes les méthodes de conception de circuits

intégrés.2 Janvier 2004 2

INFORMATION

2.1Dualité état et temps

La notion d'information correspond à la connaissance d'un état donné parmi plusieurs possibles à un

instant donné. La Figure 1 illustre cette notion avec un signal électrique.Référence haute

Référence basse

tempsTension BAS HAUT t 1t2Figure 1.- Information : état et temps.

Elle montre quil y a deux états significatifs, létat bas lorsque la tension est inférieure à une référence

basse, et un état haut lorsque la tension est supérieure à une référence haute. Le troisième état, situé

entre les références basse et haute, ne peut être utilisé comme support dinformation. Pour quil y ait

information, il faut préciser linstant auquel on regarde létat du signal. : par exemple, en t1 le signal est

haut et en t2, le signal est bas.

2.2 Quantité d'information et codage de l'informationLinformation est mesurable, avec une unité qui sappelle le bit. La formule I (bits) = log

2(N) où N est

le nombre d'états possibles donne la quantité d'information. Un bit correspond donc à la connaissance

dun état parmi deux. Par exemple, la connaissance dun état parmi 8 correspond à une quantité

dinformation de I = log2 (8) = 3 bits. Les 8 états possibles sont repérés à l'aide de 3 chiffres binaires

(ayant l'un des deux états possibles 0 ou 1), comme le montre la Table 1 : Représentation de huit états

différents. La quantité dinformation exprimée en bits étant égale au nombre de chiffres binaires

correspondants, les chiffres binaires sont appelés bits.État X

2 X1 X0

0 0 0 0

1 0 0 1

2 0 1 0

3 0 1 1

4 1 0 0

5 1 0 1

6 1 1 0

7 1 1 1

Table 1 : Représentation de huit états différentsUn mot de n bits correspond à n bits d'information, puisqu'il correspond à une configuration parmi 2

n. Mais, il faut préciser à quoi correspondent les 2 n configurations. En effet, le mot de n bits peutreprésenter une instruction machine ou un opérande, qui peut être un nombre ou un caractère. Nous

présentons brièvement le codage ou représentation des nombres et des caractères.Avant dintroduire les codages des nombres et des caractères, il est utile d'introduire la notation

hexadécimale, qui n'est pas un codage de l'information, mais une manière simplifiée d'écrire des

nombres binaires. Un nombre binaire de n bits peut être écrit à l'aide de n/4 chiffres hexadécimaux si n

est multiple de 4 (ou n/4 +1 sinon) en remplaçant chaque groupe de 4 chiffres binaires, en partant des

poids faibles, par le chiffre hexadécimal correspondant (Table 2). 2.3Représentation des nombres

La Figure 2 représente un mot de n bits.

3 Janvier 2004

n-1 n-2 i 0Figure 2 .- Mot de n bits

Chiffre

hexadécimal d 3 d 2 d 1 d 00 0 0 0 0

1 0 0 0 1

2 0 0 1 0

3 0 0 1 1

4 0 1 0 0

5 0 1 0 1

6 0 1 1 0

7 0 1 1 1

8 1 0 0 0

9 1 0 0 1

A 1 0 1 0

B 1 0 1 1

C 1 1 0 0

D 1 1 0 1

E 1 1 1 0

F 1 1 1 1

Table 2 : Notation hexadécimale

2.3.1Les entiers positifs

Un mot de n bits peut représenter tous les nombres positifs compris entre 0 et 2 n-1. di étant le chiffre binaire de rang i, un mot de n bits correspond au nombre entier décimal N = id i=0n -1 i2. Avec un octet,

on peut donc représenter tous les entiers positifs entre 0 et 255. Un mot de 32 bits permet de représenter

tous les entiers positifs entre 0 et 4 294 967 295. 2.3.2Les entiers signés

La représentation des entiers signés pose un problème lié au zéro. En effet, il y a un nombre pair de

configurations associées à n bits, à répartir entre nombres positifs, nombres négatifs et la valeur 0. Il y a

plusieurs représentations possibles des entiers signés. Dans toutes les configurations, les nombres

positifs sont représentés de la même manière, correspondant à la représentation des entiers positifs sur

n-1 bits, avec dn-1 = 0. Le bit de poids fort dn-1 est appelé le bit de signe : il est à 0 pour les nombres

positifs. a) Valeur absolue et signeDans cette représentation, le bit n-1 est le bit de signe, et les bits 0 à n-2 donnent la valeur absolue. Un

mot de n bits correspond au nombre entier décimal signé N = n-1d (-1). id i=0 n-2 i 2 , soit N = -1id i=0 n-2 i 2 quand le bit de signe est à 1 et id i=0 n-2 i 2 lorsque le bit de signe est à zéro.Un octet permet de représenter les entiers signés compris entre -127 et + 127. Il y a deux représentations

possibles du zéro, qui sont 000000002 (+0) et 100000002 (-0). Un mot de 32 bits permet de représenter

tous les entiers signés compris entre -(231-1) et 231-1, avec toujours deux zéros.

b) Entiers signés en complément à 1Dans la représentation en complément à 1, le nombre négatif -N est obtenu en remplaçant chaque

chiffre binaire d i du nombre positif N par le complément i d. (cf. l'opération complément de l'algèbre deBoole en 3.1) : les bits 1 sont remplacés par des 0 et réciproquement. Un octet permet de représenter

tous les entiers signés compris entre -127 (10000002) et +127 (011111112), avec deux zéros qui sont

00000000

2 (+0) et 111111112 (-0).

c) Entiers signés en complément à 24 Janvier 2004 Dans la représentation en complément à 2, un nombre est représenté par N = - a

n-12n-1 + iai2 i =0 n-2Lécriture en complément à 2 correspond donc à la situation où le bit de poids fort est de poids négatif.

La Table 3 donne l'ensemble des nombres en complément à 2 avec des mots de 3 bits d 2 d 1 d 0 N0 0 0 0

0 0 1 1

0 1 0 2

0 1 1 3

1 0 0 -4

1 0 1 -3

1 1 0 -2

1 1 1 -1

Table 3 : Nombres en complément à 2 sur 3 bits Un mot de n bits permet de représenter tous les entiers signés compris entre -2 n-1 et 2n-1 - 1. Il y amaintenant une seule représentation de 0 (qui est le 0 positif). Avec un octet, on représente les entiers

signés entre -128 (100000002) et +127 (011111112). La représentation en complément à 2 d'un nombre

négatif peut être obtenue à partir de la représentation en complément à 1, à laquelle on ajoute +1.

d) la représentation excès N.Lexcès N est choisi de manière à ce que la somme de lexcès et du nombre ne soit jamais négative.

Cette somme est représentée comme un nombre positif normal.La représentation en complément à 2 est la plus couramment utilisée pour larithmétique sur les

nombres entiers. Elle a lavantage de ne pas introduire de traitement particulier pour le signe dans le cas

des additions et des soustractions, et de permettre une détection facile des cas de débordement.

Les représentations en signe-valeur absolue et en complément à un ont des opérations arithmétiques

plus complexes. Elles ont aussi linconvénient davoir deux représentations de zéro. La représentation

signe-valeur absolue est utilisée pour la multiplication des mantisses des nombres flottants. Lareprésentation excès N est utilisée pour les exposants des nombres flottants. Elle permet de ramener la

comparaison dexposants de signe contraire à des comparaisons dentiers positifs. 2.3.3Représentation dite " flottante »

La représentation dite "flottante" a pour but de permettre de représenter une approximation des nombres

réels, en permettant une différence non constante entre deux nombres représentés successifs. Dans cette

représentation, un nombre est caractérisé par son signe, sa mantisse et son exposant qui est associé à

une base : +/- m.B e. En numération décimale, 1,5 x 1015 est un exemple de nombre "flottant". Enmachine, la base B utilisée est 2. Dans la norme IEEE 754 qui est la plus utilisée maintenant, la

mantisse, exprimée en signe et valeur absolue, est 1,f où 1 est implicite et f est la partie fractionnaire,

correspondant aux puissances successives de 2 -i. Lexposant est exprimé en code excès N. La Figure 3présente la représentation flottante double précision, sur 64 bits, qui est la plus couramment utilisée. La

partie exposant donne sur 11 bits la valeur de lexposant en code excès 1023. La partie fractionnaire a

52 bits. Le bit 63 donne le signe de la partie fractionnaire. Le nombre flottant double précision

correspond à (-1) signe x (1,f1f2...f52) x 2 (E-1023)La norme flottante IEEE 754 permet de représenter les nombres normalisés (bits de E différents de tous

à 0 ou tous à 1), les nombres dénormalisés (E tous à 0 et partie fractionnaire non nulle), la valeur zéro

(E tous à 0 et partie fractionnaire nulle), linfini (E tous à 1 et partie fractionnaire nulle) et des

caractères spéciaux (Not a number lorsque les bits de E sont tous à 1 et la partie fractionnaire est

différente de 0).En représentation double précision, la mantisse m est comprise entre 1 lorsque tous les bits f1 à f52 sont

à 0 et 2 - 2-

52 lorsque tous les bits f1 à f52 sont à 1. Le champ exposant E est compris entre 1 et 2046

pour les nombres normalisés. Compte tenu de l'excès 1023, l'exposant réel est donc compris entre -1022

et + 1023. Le plus petit nombre positif normalisé représentable est donc 2 -1022 et le plus grand est voisin de 2 x 21023 soit 21024.

5 Janvier 2004

051partie fractionnaire63 5262 exposant S f1f52E signe

Figure 3 .- Format flottant double précision.

La représentation simple précision sur 32 bits a 1 bit de signe, 8 bits de partie exposant (avec excès

+127) et 23 bits pour la partie fractionnaire.2.3.4

Représentation des nombres décimaux

Un certain nombre d'applications, notamment en gestion, exigent des calculs décimaux exacts, sansarrondis, ce qui implique de travailler avec des nombres décimaux. En effet, avec un nombre fixé de

bits, il est impossible de convertir de manière exacte des nombres binaires en nombres décimaux et

réciproquement. On utilise alors la représentation décimale codée binaire, dans laquelle chaque chiffre

décimal est codé avec 4 chiffres binaires, selon la Table 4. Cette représentation utilise uniquement les

chiffres décimaux de la notation hexadécimale. 2.4Représentation des caractères

La représentation des caractères est fondamentale. Les lettres de l'alphabet latin et un certain nombre de

caractères usuels sont représentés par un octet, selon un code qui est le plus souvent le code ASCII . Par

exemple, dans ce code, la lettre a est représentée par 010000002 et le chiffre 9 par 001110012.

Chiffre décimal d

3 d 2 d 1 d 00 0 0 0 0

1 0 0 0 1

2 0 0 1 0

3 0 0 1 1

4 0 1 0 0

5 0 1 0 1

6 0 1 1 0

7 0 1 1 1

8 1 0 0 0

9 1 0 0 1

Table 4 .- Décimal codé binaire

6 Janvier 2004 3

ALGÈBRE DE BOOLE ET FONCTIONS BOOLÉENNES

3.1PROPRIÉTÉS

Lalgèbre de Boole est définie sur l'ensemble E2 constitué des éléments {0,1}. Il existe une relation

d'ordre 0 < 1, et trois opérations de base. La complémentation, définie en Table 5 est une application de

E2 sur E2. Les opérations union (Table 6, gauche) appelée encore ou, max et qui est notée +, et

intersection (Table 6, droite) appelée encore et, min, qui est notée . sont des applications de E2 X E2 ->

E 2 x x 0 1 1 0Table 5 : complémentation

x y S x y S0 0 0 0 0 0

0 1 1 0 1 0

1 0 1 1 0 0

1 1 1 1 1 1

Table 6 : Union, +, ou, max Intersection, ., et, minPour tout a, b, c

?E2, les propriétés suivantes sont vérifiées :1) 0 est l'élément minimum, 1 est l'élément maximum

a.1 = a car min (a,1) = a a+0 = a car max (a,0) = a a.0 = 0 a+1 = 12) complément :

a.a=0 car min (0,1) = 0 a+a=1 car max (0,1) = 13) Commutativité

a.b = b.a a+b = b+a car les fonctions min et max sont commutatives4) Associativité

a.(b.c) = (a.b).c= a.b.c a+(b+c) = (a+b)+c= a+b+c car les fonctions min et max sont associatives5) Distributivité

a.(b+c) = a.b+a.c a+(b.c) = (a+b).(a+c)6) THÉORÈME DE MORGAN

a.b=a+b a+b=a.b La Table 7 constitue une démonstration de ce théorème. a b a b a.b a.b a+b a+b a.b a+b0 0 1 1 0 1 0 1 1 1

0 1 1 0 0 0 1 1 1 0

1 0 0 1 0 0 1 1 1 0

1 1 0 0 1 0 1 0 0 0

Table 7 : théorème de Morgan

7 Janvier 2004 3.2

OPÉRATEURS NAND ET NOR

Les opérateurs NAND et NOR ont la définition suivante.NAND (a, b) =

a.b=a+bNOR (a,b) =

a+b=a.bCes opérateurs sont fonctionnellement complets : avec un de ces opérateurs, on peut implanter les

fonctions complément, min et max de lalgèbre de Boole. La démonstration pour lopérateur NAND est la suivante : x=x.1=x.x x.y=1.x. y x+y=1.x.1.yLa Figure 4 donne la représentation symbolique des différents opérateurs, sous forme de portes logiques.

Linverseur (NOT) correspond à la fonction complémentation. Les autres portes ont le même nom que

les fonctions logiques correspondantes.NOT ET OU NAND NOR

Figure 4 : Opérateurs logiques.

La Figure 5 donne les deux représentations graphiques du théorème de Morgan. Figure 5 : Représentation graphique du théorème de MorganLes portes logiques que nous avons présentées travaillent sur les valeurs logiques 0 et 1. Elles supposent

un fonctionnement instantané, cest à dire un retard nul entre entrée et sorties. Ces portes sont

implantées avec des circuits électriques, qui travaillent sur des variables continues. Il y a toujours un

retard entre entrée et sortie. Nous présentons en 7 (Technologie et circuits logiques) la manière de

réaliser les différentes portes avec des transistors. Il est important de souligner que toutes les propriétés

de lalgèbre de Boole ne sont pas toujours vérifiées avec les circuits réels. Les deux propriétés

a.a=0 eta+a=1 ne sont pas toujours vérifiées. La Figure 6 montre quà cause des temps de retard entre

lentrée et la sortie dun inverseur, il y a deux périodes pendant lesquelles les deux relations ne sont pas

vérifiées : cest le cas lorsque E = E. Cette situation correspond à ce que lon appelle un aléa. Lessignaux des circuits physiques ne sont donc valides que lorsque les lois de lalgèbre de Boole sont

vérifiées, cest à dire en dehors des aléas. ES=E E S=E E=E E=E Figure 6 : Les aléas liés aux temps de retard dans un inverseur 3.3FONCTIONS BOOLÉENNES

Dans le cas général, les fonctions booléennes sont une application de E i x Ej x Ek ..x Ep -> E2 où Ei={0, 1, 2,...,i-1}. Les variables dentrée ont un nombre fini de valeurs entières. La Table 8 donne la table

8 Janvier 2004 de vérité dune fonction booléenne pour laquelle la variable x est binaire et la variable y est ternaire (3

états possibles).

x y S 0 0 1 0 1 0 0 2 1 1 0 0 1 1 0 1 2 1Table 8 : Exemple de fonction booléenne

Comme les fonctions utilisées pratiquement ont des variables dentrée de même nature que les variables

de sortie, on se restreint au cas particulier des fonctions booléennes applications de E2 x E2 x E2...x E2

-> E2. La Table 9 donne lexemple dune telle fonction de deux variables x et y. Cette manière de

représenter une fonction booléenne est appelée table de vérité. Les tables de vérité illustrent les deux

problèmes rencontrés lors du traitement dune fonction booléenne : il faut être capable de repérer une

entrée de la table, et il faut être capable dassocier une valeur de la fonction à chaque entrée de la table.

x y S m 00 0 0

m 10 1 1

m 21 0 1

m 31 1 0

Table 9 : Exemple de fonction booléenne de deux variables. Il existe différentes manières d'exprimer une fonction booléenne. 3.3.1Forme disjonctive normale

A chaque entrée de la table, on associe une variable binaire mi appelée terme produit (minterm).. m0 est

associé à la ligne 0, m1 est associé à la ligne 1, etc.

mquotesdbs_dbs29.pdfusesText_35[PDF] Situation sanitaire exceptionnelle

[PDF] La Palestine : vers un État sans nation? - Érudit

[PDF] E Les graphes probabilistes - Lycée d 'Adultes

[PDF] LA NOTION D ETAT-NATION

[PDF] États financiers

[PDF] etats financiers ohada - eRegulations Garoua

[PDF] LIASSE SYSTEME ALLEGE 1ère partiexls - eRegulations Togo

[PDF] etats financiers et notes aux etats financiers au 31 - BNA CAPITAUX

[PDF] 28 La Révolution de 1789 - Académie de Nancy-Metz

[PDF] Conditions particulières d 'admission pour les programmes - UQAM

[PDF] Corrigé du bac S Histoire-Géographie 2015 - Centres - Sujet de bac

[PDF] Cours 3 : États-Unis - Brésil : rôle mondial, dynamiques territoriales

[PDF] Etats-Unis - Brésil, rôle mondial, dynamiques territoriales

[PDF] ? Comment se manifeste la puissance américaine