Examen dEléments de Génie Logiciel

Examen dEléments de Génie Logiciel

Licence 3 Informatique 2006/2007. 14/05/2007. Examen d'Eléments de Génie Logiciel. Durée : 2 heures. Seuls documents autorisés : mémento UML et mémento OCL.

Site Web

Site Web

27 juin 2011 au Campus principal situé à Sherbrooke

Page 1/2 USTHB 04/02/2013 Faculté dElectronique et Informatique

Page 1/2 USTHB 04/02/2013 Faculté dElectronique et Informatique

4 févr. 2013 Département d'Informatique. Examen de rattrapage. Module : Génie Logiciel. (Niveau : Licence 3 – ACAD / Section A-B-C). (Durée 1: ...

Département Informatique de lIUT de lUniversité Bordeaux 1

Département Informatique de lIUT de lUniversité Bordeaux 1

Cours d'Analyse et Conception des Systèmes d'Information. (d'Outils et Modèles pour le Génie Logiciel). 7 novembre 2007. Olivier Guibert

D03-MI-2009-2013-Genie Logiciel

D03-MI-2009-2013-Genie Logiciel

Un diplômé de master académique en Informatique de la connaissance et intelligence Artificielle est censé devenir : Un expert dans le développement de logiciels

Cours de Génie Logiciel (avec exercices résolus) 1ere Année

Cours de Génie Logiciel (avec exercices résolus) 1ere Année

Logiciel » en faveur les étudiants de la 1ere année Master (spécialité GL) au niveau du département informatique de l?université de Tiaret.

Analyse et Conception du Système dInformation (Merise)

Analyse et Conception du Système dInformation (Merise)

développement de systèmes d'information du génie logiciel et de la Au sens informatique

PLANNING DES EXAMENS S1 2e Année LICENCE Lieu dexamens

PLANNING DES EXAMENS S1 2e Année LICENCE Lieu dexamens

13 févr. 2022 Faculté des Mathématiques et Informatique. Département d'Informatique. Année Universitaire 2021/2022. PLANNING DES EXAMENS S1.

Département Sécurité et Technologies Informatiques

Département Sécurité et Technologies Informatiques

19 mai 2022 Crédits ECTS : 12. Principes de la programmation. Elément Constitutif : Coefficient : 0.5. Initiation au Génie Logiciel. Tronc Commun.

Examen de synthèse

Examen de synthèse

Département de génie informatique et génie logiciel. INF3500 : Conception et réalisation de systèmes numériques. Examen intra. Vendredi 25 février 2011.

École Polytechnique de Montréal page 1/12 Département de génie informatique et génie logiciel

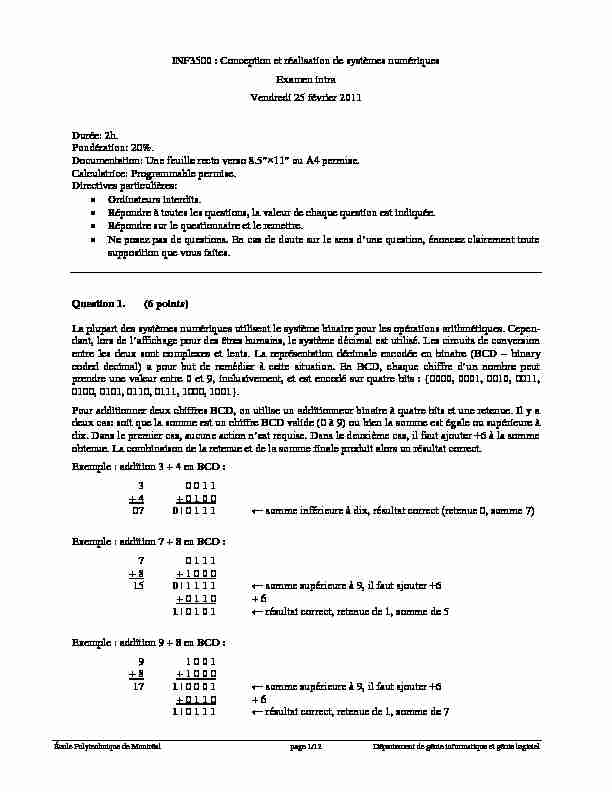

INF3500 : Conception et réalisation de systèmes numériquesExamen intra

Vendredi 25 février 2011

Durée: 2h.

Pondération: 20%.

Documentation:

Calculatrice: Programmable permise.

Directives particulières:

Ordinateurs interdits.

Répondre à toutes les questions, la valeur de chaque question est indiquée.Répondre sur le questionnaire et le remettre.

supposition que vous faites.Question 1. (6 points)

La plupart des systèmes numériques utilisent le système binaire pour les opérations arithmétiques. Cepen-

entre les deux sont complexes et lents. La représentation décimale encodée en binaire (BCD binary

coded decimalprendre une valeur entre 0 et 9, inclusivement, et est encodé sur quatre bits : {0000, 0001, 0010, 0011,

0100, 0101, 0110, 0111, 1000, 1001}.

Pour additionner deux chiffres BCD, on utilise un additionneur binaire à quatre bits et une retenue. Il y a

deux cas: soit que la somme est un chiffre BCD valide (0 à 9) ou bien la somme est égale ou supérieure à

obtenue. La combinaison de la retenue et de la somme finale produit alors un résultat correct.Exemple : addition 3 + 4 en BCD :

3 0 0 1 1

+ 4 + 0 1 0 007 0 | 0 1 1 1 ĸ

Exemple : addition 7 + 8 en BCD :

7 0 1 1 1

+ 8 + 1 0 0 015 0 | 1 1 1 1 ĸ

+ 0 1 1 0 + 61 | 0 1 0 1 ĸ

Exemple : addition 9 + 8 en BCD :

9 1 0 0 1

+ 8 + 1 0 0 017 1 | 0 0 0 1 ĸ

+ 0 1 1 0 + 61 | 0 1 1 1 ĸ

INF3500 contrôle périodique 25 février 2011École Polytechnique de Montréal page 2/12 Département de génie informatique et génie logiciel

a. (3 points) Dà un chiffre.Vous pouvez utiliser des opérations logiques et arithmétiques (mais pas la division ni le modulo), la com-

paraison, des multiplexeurs, décodeurs et encodeurs, et toute autre porte logique de base. Identifiez bien

chaque bloc et donnez la largeur en bits de tous les signaux. Votre circuit doit être purement combinatoi-

Solution :

>= 10? additionneurà 4 bits

oper1 (4 bits) oper2 (4 bits) cin somme intermédiaire (4 bits) retenue (1 bit) additionneurà 4 bits

0 somme (4 bits) cout 10 60bit unique bus de 4 bits INF3500 contrôle périodique 25 février 2011

École Polytechnique de Montréal page 3/12 Département de génie informatique et génie logiciel

b. (3 points) Donnez le code VHDL correspondant à votre diagramme.Solution :

library IEEE; use ieee.std_logic_1164.all; use ieee.numeric_std.all; entity addBCD is port ( oper1, oper2 : in unsigned(3 downto 0); somme : out unsigned(3 downto 0); cout : out std_logic end addBCD; architecture arch1 of addBCD is begin process(oper1, oper2) variable t : unsigned(4 downto 0); begin t := ('0' & oper1) + ('0' & oper2); if (t > 9) then t := t + 6; end if; somme <= t(3 downto 0); cout <= t(4); end process; end arch1; INF3500 contrôle périodique 25 février 2011École Polytechnique de Montréal page 4/12 Département de génie informatique et génie logiciel

Question 2. (4 points)

Considérdu code VHDL partiel.

library IEEE; use IEEE.std_logic_1164.all; entity controle201101Q2 is port ( reset, CLK : in STD_LOGIC; x : in STD_LOGIC_VECTOR(1 downto 0); sortie : out STD_LOGIC end controle201101Q2; architecture arch of controle201101Q2 is -- Votre code ici -- Solution type type_etat is (S1, S2, S3, S4); signal etat : type_etat := S1; begin -- Votre code ici -- Solution process(CLK, reset) is begin if (reset = '0') then etat <= S1; elsif (rising_edge(CLK)) then case etat is when S1 => if x = "00" then etat <= S3; elsif x = "01" then etat <= S2; end if; when S2 | S3 => if x = "10" then etat <= S4; elsif x = "11" then etat <= S1; end if; when S4 => etat <= S1; when others => etat <= S1; end case; end if; end process; process(x, etat) begin case etat is when S1 | S4 => sortie <= '1'; when others => sortie <= '0'; end case; end process; end arch; S2Sortie <= 0

S4Sortie <= 1

S3Sortie <= 0

S1Sortie <= 1

x=00 x=01 x=10 x=10 reset x=11 x=11 INF3500 contrôle périodique 25 février 2011École Polytechnique de Montréal page 5/12 Département de génie informatique et génie logiciel

Question 3. (2 points)

-opérations suivantes.(où sll X, Y veut dire : faire un décalage logique vers la gauche du registre X du nombre de bits spécifié

par le registre Y)Une solution possible :

D CLK Q charge S K1 D CLK Q A décaleur D CLK Q B compte D CLK Q CUne solution possible :

INF3500 contrôle périodique 25 février 2011École Polytechnique de Montréal page 6/12 Département de génie informatique et génie logiciel

Question 4. (2 points)

Considérez le code VHDL suivant.

Expliquez les étapes suivies par un synthétiseur pour interpréter le code et inférer les structures matériel-

les nécessaires pour réaliser la fonction décrite. library ieee; use ieee.std_logic_1164.all; entity decodeur38 is port(A : in std_logic_vector(2 downto 0);

F: out std_logic_vector(7 downto 0)

end decodeur38; architecture flotDeDonnees of decodeur38 is begin with A select F <= "00000001" when "000",quotesdbs_dbs29.pdfusesText_35[PDF] Formulaire d 'inscription - Jury central - Connaissance de base en

[PDF] Gymnase Auguste Piccard

[PDF] Page 1 Examen de fin d 'études Secondaires HISTOIRE ET

[PDF] Examen Histoire Secondaire 4 2016

[PDF] Technologies de Web Exercices et contrôles corrigés - Université

[PDF] Correction d 'examen

[PDF] Calendrier des examens Janvier 2016 10 - IHEC

[PDF] Licence de Biologie 2ème année

[PDF] QCM immuno annales internat 2013 - Faculté de Droit de Caen

[PDF] Examen - Université de Biskra

[PDF] Corrigé Examen d 'informatique - SoC

[PDF] Corrigé Examen d informatique - SoC

[PDF] Cnam - Intec - Diplôme supérieur de comptabilité et de gestion

[PDF] Annales d examen - BU Toulon