FEUILLE DEXERCICES : Logique séquentielle.

FEUILLE DEXERCICES : Logique séquentielle.

8 FONCTION COMPTEUR ASYNCHRONE MODULO X A BASCULES JK". 1. Sur quel front fonctionnent les bascules ? 2. A quel niveau logique les entrées /R sont elles

TD systèmes logiques.pdf

TD systèmes logiques.pdf

Exercice 2: Développez un circuit logique (transcodeur) muni de 3 variables d'entrée (AB

SCIENCES DE LINGENIEUR

SCIENCES DE LINGENIEUR

• Logique programmée à base d'ordinateur de microcontrôleur ou d'automate programmable Electronique Numérique logique séquentielle

Systèmes Logiques (2) Logique séquentielle

Systèmes Logiques (2) Logique séquentielle

Dans les circuits séquentiels asynchrones les sorties changent d'états dès qu'Il 4.5.3 Exercice. Soit le montage suivant : Compléter le chronogramme de D et ...

ELA114 : conception numérique en VHDL

ELA114 : conception numérique en VHDL

seule solution efficace pour éviter ce genre de problème est d'utiliser la logique séquentielle à l'aide d'une feuille Excel on estimait la consommation ...

Exercices et solutions

Exercices et solutions

7 mai 2010 Temps de lecture séquentielle de la table (hypothèse de lecture anticipée d ... A.19 Chapitre 19 - Conception logique d'une base de données ...

Conservatoire National des

Conservatoire National des

Une machine d'état est ainsi appelée car la logique séquentielle qui l On étudie dans cet exercice la réalisation d'un compteur binaire ainsi que la meilleure.

BASES DE DONNÉES ET MODÈLES DE CALCUL

BASES DE DONNÉES ET MODÈLES DE CALCUL

logique. 72. 5.2.7 Données extraites et données dérivées. 76. 5.2.8 Les fonctions SQL ... d'une feuille de calcul constitue un seul et même exercice intellectuel ...

BCI - TPSP - Électronique Numérique Intégrée

BCI - TPSP - Électronique Numérique Intégrée

26 sept. 2005 D'une façon complémentaire à la logique combinatoire la logique séquentielle permet d'orga- niser les calculs booléens dans le temps. Par ...

FEUILLE DEXERCICES : Logique séquentielle.

FEUILLE DEXERCICES : Logique séquentielle.

FEUILLE D'EXERCICES : Logique séquentielle. FONCTION DECOMPTEUR ASYNCHRONE A BASCULE D.. ... FONCTION COMPTEUR ASYNCHRONE MODULO 10 A BASCULE D..

Exercice corrigé bascule d pdf

Exercice corrigé bascule d pdf

FEUILLE D'EXERCICES : Logique séquentielle. la lampe s'éteint en appuyant sur le Exercice 2 : A chaque front montant de l'horloge d'une bascule D ...

Bascules Registres

Bascules Registres

Mémoires •Circuit asynchrone : les

Exercice 1 : Exercice 2 :

Exercice 1 : Exercice 2 :

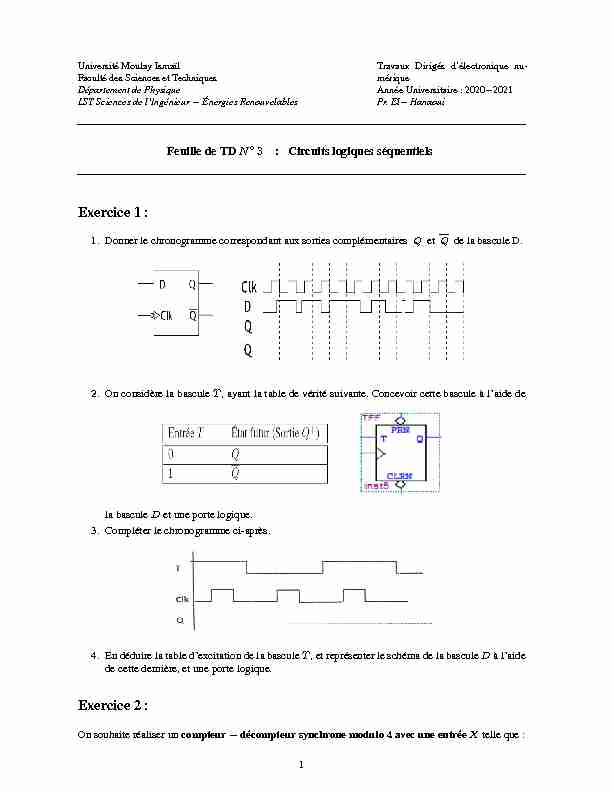

Feuille de TD N? 3 : Circuits logiques séquentiels. Exercice 1 : 1. Donner le chronogramme correspondant aux sorties complémentaires Q et Q de la bascule D

LOGIQUE SEQUENTIELLE

LOGIQUE SEQUENTIELLE

Les circuits logiques examinés jusqu'à présent ont la propriété de fournir en Un système séquentiel est dit synchrone lorsque le changement d'état des ...

Conservatoire National des

Conservatoire National des

La logique séquentielle (avec mémoire) sera vue au chapitre suivant. Vous verrez le schéma interne de cet additionneur en exercice dirigé.

Exercices et problèmes dalgorithmique

Exercices et problèmes dalgorithmique

fondements mathématiques de l'algorithmique notamment des logiques d'exécution. Avec les structures séquentielles et les approches itératives

Management des compétences et organisation par projets: une

Management des compétences et organisation par projets: une

30 août 2012 d'accepter d'évaluer ce travail et pour l'investissement que la ... compétences de « logique compétences »

GUIDE PÉDAGOGIQUE POUR LE PRIMAIRE

GUIDE PÉDAGOGIQUE POUR LE PRIMAIRE

à l'intérieur d'une démarche d'enseignement en français langue maternelle. Ainsi les (acétates)

SCIENCES DE LINGENIEUR

SCIENCES DE LINGENIEUR

d'expression d'organisation de travail et de recherche méthodique ; flip-flop) sont les éléments de base de la logique séquentielle.

Université Moulay Ismaïl

Faculté des Sciences et Techniques

Département de Physique

LST Sciences de l"IngénieurÉnergies RenouvelablesTravaux Dirigés d"électronique nu- mériqueAnnée Universitaire : 20202021

Pr. ElHanaouiFeuille de TDN3: Circuits logiques séquentielsExercice 1 :1. Donner le chronogramme correspondant aux sorties complémentairesQetQde la bascule D.2. On considère la basculeT, ayant la table de vérité suivante. Concevoir cette bascule à l"aide dela basculeDet une porte logique.

3. Compléter le chronogramme ci-après.4. En déduire la table d"excitation de la basculeT, et représenter le schéma de la basculeDà l"aide

de cette dernière, et une porte logique.Exercice 2 :

On souhaite réaliser uncompteurdécompteur synchrone modulo4avec une entréeXtelle que : 1EntréeXFonction

0Comptage

1Décomptage

1. Combien de basculesJKsont nécessaires?

2. Donner le graphe d"états, puis établir la table de vérité du circuit.

3. Déterminer les équations des entréesJiKides bascules.

4. Faire le schéma.

Exercice 3 :

On considère le circuit logique séquentiel suivant.1. Donner les équations d"états, et l"expression de la sortie.

2. En déduire la table des états, et le graphe correspondant.

3. Préciser le type de machine en question.

Exercice 4 : Conception

On veut concevoir un système d"ouverture de porte avec code d"accès. La machine reçoit en entréeX

une série de chiffres tapée sur un clavier numérique. Si la machine reçoit la bonne séquence de chiffres

0;2;3;5, la porte est ouverte grâce au signal de sortie.

1. Dessiner le diagramme des états selon une forme demachine de Moore.

2. Transformer cette machine en unemachine de Mealy.

Exercice 5 :

La figure 1, montre un compteurdécompteur4bits. SiD= 0etEnable= 0, le système évolue. Il est maintenu lorsqueEnable= 1. On vous demande de concevoir un compteur Modulo12, en utilisant ce système, et1ou+s portes de votre choix. 2FIGURE1 -

Exercice 6 : Registre universel 4 bits

Considéronsun registre universel 4 bits, représenté sur la figure 2.FIGURE2 - Son symbole est montré sur la figure 3.FIGURE3 - Ce registre étant décrit par la table de vérité suivante (CNT=Q). 3 CLRHC 1C0FonctionQ

+3Q+2Q+1Q+00XXXRAZ asynchrone0 0 0 01#00MaintienQ

3Q2Q1Q01#01Décalage à droiteRi Q

3Q2Q11#10Décalage à gaucheQ

2Q1Q0Le1#11Chargement==I

3I2I1I01. Concevoir à l"aide de ce registre, un système logique qui génère la séquence suivante :

9!3!7!12!9:::

2. Détailler la démarche suivie pour réaliser la fonctionf(x) = 2x;xétant un entier de taille

4bits.

Problème : Synthèse d"un compteur synchrone (Extrait de l"examen de session normale 2020) (laissé en exercice)La fonction comptage est l"une des plus importantes de l"électronique numérique. Rares sont les designs

des circuits logiques qui n"en comportent pas un grand nombre. Le principe est simple : à chaque coup

d"horloge CLK, la sortie d"un compteur est incrémentée.On souhaite réaliser un compteur Modulo8à partir denbasculesT, pilotées par le même signal

d"horlogeCLK. Ce compteur possède des fonctions supplémentaires :CLRN(pour remettre à zéro

l"état du compteur), etENABLE(pour autoriser le comptage ou mémoriser la valeur précédente). La

table de vérité du compteur est indiquée sur la figure ci-dessous.1Combien de basculesTsont nécessaires?

2Établir la table de vérité de ce compteur.

3Donner les équations des entréesTi(i= 0;1;n1)des différentes bascules.

4En déduire le schéma de ce compteur.

5Montrer comment adjoindre quelques portes à ce module afin de créer un compteur Modulo6

avec RESET asynchrone.6Proposer un schéma d"un système logique permettant d"accomplir la fonction suivante, en utili-

sant un circuit usuel non arithmétique à préciser, et les compteurs déjà conçus.ModeCFonction

0Comptage modulo 6

1Comptage modulo 8

4 Corrigé de Feuille de TDN3: Circuits logiques séquentielsExercice 1 :1. Les chronogrammes correspondant aux sorties complémentairesQetQde la bascule D,

sachant que cette dernière réagit au front négatif, sont comme suit :Nous avons appliqué ici :Q+=D.

2. Rappelons la table de vérité associée à la basculeT. Cette TV peut être encore réarrangée dela façon portée au tableau 1. En ce qui concerne la bascule la basculeD, sa TV est égalementClkQ Q+T

"0 00 "0 11 "1 01 "1 10TABLE1 -

rappelée dans le tableau 2. Les deux TV sont équivalents (fonctions équivalentes); on a alors :Clk DQQ

+DQ"0 000 "0 101 "1 011 "1 110TABLE2 -

5 T=DQ, autrement écrit :D=TQ. La Figure 4 présente le schéma équivalent de la basculeT, obtenu à partir d"une basculeD.FIGURE4 -3. Le chronogramme en question est ci-après.4. Même démarche que2.

Exercice 2 :

Réalisons uncompteurdécompteur synchrone modulo4avec une entréeXtelle que :EntréeXFonction

0Comptage

1Décomptage

1. Nombre de basculesJKnécessaires? On a4 = 22états qui sont :0;1;2;3, donc il nous faut2

basculesJK.2. Le graphe d"états est présenté sur La figure 5.

La table de transition d"états relative au comptage (X= 0), est présentée dans le tableau 3.

Celle associée au décomptage (X= 1), est présentée dans le tableau 4. L"encodage des états

est présenté dans le tableau 3 (C0,C1,C2etC3ont pour codes respectifs" 00 "," 01 ", " 10 "et" 11 ").3. Déterminons les équations des entréesJiKides bascules JK pour conditionner l"évolution fu-

tur de l"état du système. Faisons appel alors aux tableaux de Karnaugh 5 et 6, qui donnent les solutions minimales respectives pourJ0K0, etJ1K1. On tire : J0= 1 ;K0= 1

De même, On obtient :

J1=XQ0;K1=XQ0

6 FIGURE5 -État Présent Etat Futur Entrées Bascule JK Sortie (X= 0)Q0;PQ1;PQ

0;FQ1;FJ

0;PK0;PJ

1;PK1;PCNT

C 00 0C10 1100

C 10 1C21 0 11 1

C 21 0C31 11 02

C 31 1C00 0 1 13

TABLE3 -État Présent Etat Futur Entrées Bascule JK Sortie (X= 1)Q0;PQ1;PQ

0;FQ1;FJ

0;PK0;PJ

1;PK1;PCNT

C 00 0C31 1110

C 31 1C21 0 1 03

C 21 0C10 11 12

C 11 0C00 0 10 1

TABLE4 -XQ0Q10 00 11 11 0

01 1 11

11 1 11

TABLE5 -XQ0Q10 00 11 11 0

00 1 1 0

11 0 0 1

TABLE6 -

4. Le schéma correspondant aucompteurdécompteur synchrone modulo4est présenté sur la

figure 6. 7FIGURE6 -

La figure 7 montre le rapport de simulation correspondant.FIGURE7 -Exercice 3 :

Analysons le circuit logique séquentiel suivant.81. Donnons les équations d"états, ainsi que l"expression de la sortie. On a :

J 0=X+Q1;K0= 1

J1=Q0;K1=X+Q0

Y=XQ0Q1+XQ0Q1

2. Table des états (À faire). La figure 8 montre le graphe des états correspondant.FIGURE8 -

3. Dans cet exercice, la machine analysée est de type MEALY. En effet,

Y=func(X;E:P(Q0;Q1))

Exercice 4 : Conception

Concevons un système d"ouverture de porte avec code d"accès. La machine reçoit en entréeXune

série de chiffres tapée sur un clavier numérique. Si la machine reçoit la bonne séquence de chiffres

0;2;3;5, la porte est ouverte grâce au signal de sortie. Pour ce faire,

1. Rappelons d"abord les deux architectures des machines à états finis (FSM). La figure 9 montre

celle de lamachine de Moore. Celle de lamachine de Mealyest présentée sur la figure 10.FIGURE9 -

Dessinons ensuite, le diagramme des états selon la1ereforme. La figure 11 montre le graphe desétats correspondant.

2. Procédez de la même façon pour transformer cette machine en unemachine de Mealy.

N.B :Dans ce cas, vous aurez1état de moins.

9FIGURE10 -FIGURE11 -

Exercice 5 :

Reprenons la figure du compteurdécompteur4bits.Le système évolue siD= 0etEnable= 0, c"est à dire compte0000 ; 0001 ;:::1011 ;:::1111.

Il stocke la dernière valeur siEnable= 1. Comment alors concevoir à partir de ce système, un

compteur Modulo12? Dans ce cas, le compteur aura1011comme valeur maximale. Ensuite après, ilfaut ordonner au système, grâce à l"entréeLoad, le chargement de la valeur0000. La figure 12 montre

le schéma du circuit résultant. 10FIGURE12 -

Exercice 6 : Registre universel 4 bits

Considérons leregistre universel 4 bits, symbolisé par,Ce registre étant décrit par la table de vérité ci- après (CNT=Q).CLRHC

1C0FonctionQ

+3Q+2Q+1Q+00XXXRAZ asynchrone0 0 0 01#00MaintienQ

3Q2Q1Q01#01Décalage à droiteRi Q

3Q2Q11#10Décalage à gaucheQ

2Q1Q0Le1#11Chargement==I

3I2I1I01. Concevons à l"aide de ce registre, un système logique qui génère la séquence suivante :

9!3!7!12!9:::

La table de transition est comme suit : L"encodage des états est présenté dans le même tableau

(C9,C3,C7etC12ont pour codes respectifs" 1 00 1 "," 0 01 1 "," 0 11 1 "et" 1 10 0 "). Les équations des entrées du registre74194permettant de conditionner l"évolution futur del"état du système, sont telles que :C1Le= 1 1. Il reste à déterminer celle de l"entréeC0en

11 État Présent État Futur Entrées 74194 Sortie Q3;PQ2;PQ1;PQ0;PQ

3;FQ2;FQ1;FQ0;FC

1C0Le RiCNT

C91 0 0 1C

30 0 1 11019

C30 0 1 1C

70 1 1 11 0 13

C70 1 1 1C

121 1 0 011 7

C121 1 0 0C

91 0 0 11 0 112

utilisant le tableau de Karnaugh ci- après, qui donne en fait la solution minimaleC0=Q0Q2. La figure 13 montre le schéma du circuit en question.Q3Q2Q1Q00 00 11 11 0

0 00 0 11 1 10 1 00quotesdbs_dbs29.pdfusesText_35[PDF] Examen 1 : QCM et interprétations

[PDF] PLANNING DES EXAMENS DE RATTRAPAGE DE S2 FILIERE

[PDF] Examen Matière : Marketing International - L 'ENT de IGA Rabat

[PDF] Première LMD ST (S1) ~ Faculté des Sciences (Univ Tlemcen)

[PDF] Université des Sciences et de la Technologie Houari - usthb

[PDF] Épreuves uniques - Enseignement secondaire, 2e cycle

[PDF] IMM 5753F : Demande d 'examen médical - Citoyenneté et

[PDF] Les métiers des Sciences

[PDF] Microscopie en bacteriologie - Direction des laboratoires

[PDF] Calendrier Primaire 2017-2018

[PDF] Épreuve unique - Enseignement secondaire, 2e cycle - Histoire et

[PDF] Épreuves uniques - Enseignement secondaire, 2e cycle - Science et

[PDF] coproculture - XLABS laboratoire

[PDF] Nederlands - vwo: vakspecifieke informatie centraal examen 2016