COMBINATIONAL LOGIC CIRCUITS

COMBINATIONAL LOGIC CIRCUITS

Jan 8 2016 Identify “Don't care” conditions and use them in truth tables. □. Use K maps to generate the simplest SOP form from a truth table. The ...

Design and implementation of carry Look ahead generator in

Design and implementation of carry Look ahead generator in

Feb 17 2021 Figure 13 Logic circuit of carry lookahead generator. The reversible gates are ... Table 2 Truth table for carry lookahead generator. The carry ...

Analyzing ChatGPTs Aptitude in an Introductory Computer

Analyzing ChatGPTs Aptitude in an Introductory Computer

Apr 14 2023 what logic function it represents and generate Boolean equations from the truth tables. ... • Recognize logic gate diagrams and what combinatorial ...

QCA Based Design of Reversible Parity Generator and Parity

QCA Based Design of Reversible Parity Generator and Parity

Jun 22 2023 are some characteristics of a reversible logic circuit. However

10-MINUTE TUTORIAL DIGITAL LOGIC CIRCUIT MODELING AND

10-MINUTE TUTORIAL DIGITAL LOGIC CIRCUIT MODELING AND

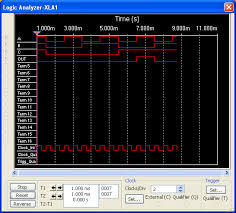

generate a truth table for the circuit) by manually toggling the inputs. Figure 7. INTERACTIVE_DIGITAL_CONSTANT sources connected to circuit inputs. Page 8 ...

On the existence of strong proof complexity generators

On the existence of strong proof complexity generators

The τ-formulas determined by this generator state circuit lower bounds for particular Boolean functions: τ(ttsk)b ∈ TAUT iff the function with truth-table b

Design And Simulation of An Electro-Optic Even Parity Bit Error

Design And Simulation of An Electro-Optic Even Parity Bit Error

Apr 30 2021 In a 3-bit even parity bit error generator logic circuit

Design and Optimization of Sequence Generator Using N-N

Design and Optimization of Sequence Generator Using N-N

May 3 2023 reversible logic gates are DOUBLE FEYNMAN gate

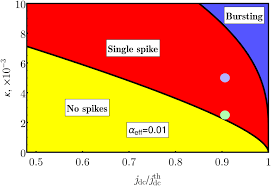

Ultra-fast logic devices using artificial “neurons” based on

Ultra-fast logic devices using artificial “neurons” based on

Sep 27 2018 The logic “truth” table for the AFM FULL-ADDER comprising three AFM ... Q-gate truth table. 1st input. 2nd input. 3rd input. Output. (Blue).

Simulation Of Analog And Digital Circuits With The Electronic

Simulation Of Analog And Digital Circuits With The Electronic

In the fourth example the Logic Converter is used to construct a Combinational Logic circuit from a Truth Table. Next

CHAPTER 3 Boolean Algebra and Digital Logic

CHAPTER 3 Boolean Algebra and Digital Logic

Truth tables can be readily rendered into Boolean logic circuits. Assuming we are using odd parity the truth table for a parity generator for a 3-bit.

COMBINATIONAL LOGIC CIRCUITS

COMBINATIONAL LOGIC CIRCUITS

Jan 8 2016 Design simple logic circuits without the help of a truth table. ... for any of the four possible input conditions

Parity Generator and Parity Checker

Parity Generator and Parity Checker

A parity generator is a combinational logic circuit that generates the parity truth table of even parity generator in which 1 is placed as parity bit in ...

DIGITAL CIRCUITS IMPLEMENTATION ON RPGA SIMULATOR

DIGITAL CIRCUITS IMPLEMENTATION ON RPGA SIMULATOR

Programmable Logic Array and Field Programmable Gate Array. design entry of reversible circuit Truth table generator

CS270 Recitation 4 “Digital Logic Simulation using Logisim”

CS270 Recitation 4 “Digital Logic Simulation using Logisim”

Generate the truth table with Logisim by the menu item “Projects-. >Analyze Circuit” and viewing the Table tab. Does it match the one you filled in above?

Gray-code adder with parity generator – a novel quantum-dot

Gray-code adder with parity generator – a novel quantum-dot

electronic circuits such as wires logic gates

CHAPTER 3 Boolean Algebra and Digital Logic

CHAPTER 3 Boolean Algebra and Digital Logic

Truth tables can be readily rendered into Boolean logic circuits. Assuming we are using odd parity the truth table for a parity generator for a 3-bit.

Automatic Generation Of Test Cases For High MCDC Coverage

Automatic Generation Of Test Cases For High MCDC Coverage

We generate test cases according to the MCDC criteria to show indepen- Truth table for 2 input xor gate is shown in Table 2.3

Digital Electronics Part I – Combinational and Sequential Logic

Digital Electronics Part I – Combinational and Sequential Logic

How digital logic gates are built using transistors Referring back to the truth table for f we can ... of the full-adder blocks

[PDF] Logic gates Logic gates and truth tables - Washington

[PDF] Logic gates Logic gates and truth tables - Washington

Logic gates and truth tables (con't) Mapping Boolean expressions to logic gates Mapping truth tables to logic gates ? Given a truth table

Truth Table Generator - Create Logical Truth Tables Instantly

Truth Table Generator - Create Logical Truth Tables Instantly

Create truth tables with this free truth table generator online This tool helps you solve and get results of boolean expressions with logic symbols quickly

[PDF] COMBINATIONAL LOGIC CIRCUITS

[PDF] COMBINATIONAL LOGIC CIRCUITS

8 jan 2016 · Use K maps to generate the simplest SOP form from a truth table The Karnaugh map (K map) is a graphical tool used to simplify a logic equa-

[PDF] Parity Generator and Parity Checker

[PDF] Parity Generator and Parity Checker

A parity generator is a combinational logic circuit that generates the parity truth table of even parity generator in which 1 is placed as parity bit in

Truth table generator (0E9EA6)

Truth table generator (0E9EA6)

Truth table generator Our goal is to use the translated formulas to Let us generate a truth table for the NOT gate using the logic gate calculator

Parity Generator and Parity Check - ElectronicsHub

Parity Generator and Parity Check - ElectronicsHub

A Parity Generator is a combinational logic circuit that generates the The truth table of the odd parity generator can be simplified by using K-map as

Constructing Truth Tables for Combinational Logic Circuits - YouTube

Constructing Truth Tables for Combinational Logic Circuits - YouTube

7 mar 2019 · https://engineers academy/product-category/level-4-higher-national-certificate-hnc-courses/This Durée : 9:35Postée : 7 mar 2019

Logic Gates Truth Tables Boolean Algebra AND OR NOT NAND

Logic Gates Truth Tables Boolean Algebra AND OR NOT NAND

22 jan 2021 · This electronics video provides a basic introduction into logic gates truth tables and Durée : 54:07Postée : 22 jan 2021

[PDF] Logic Gates and truth tables

[PDF] Logic Gates and truth tables

Logic gates may be combined to form logic gate diagrams that perform more complicated logical operations Truth tables are used to show the states of each

4-1 sum-of-Products Form

4- 2 simplifying Logic Circuits 4- 3Algebraic simplification

4- 4Designing Combinational

Logic Circuits

4- 5Karnaugh Map Method

4- 6Exclusive-OR and Exclusive-NOR Circuits

4- 7Parity Generator and Checker

4- 8Enable/Disable Circuits

4- 9Basic Characteristics of Digital ICs

outline C o mbinati o nal lo gi C Cir C uitsChapter 4

4- 10Troubleshooting Digital

systems 4- 11Internal Digital IC Faults

4- 12External Faults

4- 13Troubleshooting Prototyped Circuits

4- 14Programmable Logic Devices

4- 15Representing Data in HDL

4- 16Truth Tables Using HDL

4- 17 Decision Control structures in HDLM04_WIDM0130_12_SE_C04.indd 1361/8/16 8:38 PM 137Chapter outComes

Upon completion of this chapter, you will be able to: Convert a logic expression into a sum-of-products expression. Perform the necessary steps to reduce a sum-of-products expression to its simplest form. Use Boolean algebra and the Karnaugh map as tools to simplify and design logic circuits. Explain the operation of both exclusive-OR and exclusive-NOR circuits. Design simple logic circuits without the help of a truth table.Describe how to implement enable circuits.

Cite the basic characteristics of TTL and CMOS digital ICs. Use the basic troubleshooting rules of digital systems. Deduce from observed results the faults of malfunctioning combina tional logic circuits. Describe the fundamental idea of programmable logic devices (PLDs). Describe the steps involved in programming a PLD to perform a simple combinational logic function.Describe hierarchical design methods.

Identify proper data types for single-bit, bit array, and numeric value � variables. Describe logic circuits using HDL control structures IF/ELSE, IF/ELSIF, and CASE.

Select the appropriate HDL control structure for a given problem. introDuCtion In Chapter 3, we studied the operation of all the basic logic gates, and� we used Boolean algebra to describe and analyze circuits that were made up � of combinations of logic gates.These circuits can be classified as

combi national logic circuits because, at any time, the logic level at the output depends on the combination of logic levels present at the inputs. A comb�i national circuit has no memory characteristic, so its output depends only on the current value of its inputs.In this chapter, we will

continue our study of combinational circuits.To start, we will go

further into the simplification of logic circuits. Two methods will be used: one uses Boolean algebra theorems; the other uses �a mapping technique. In addition, we will study simple techniques for design ing combinational logic circuits to satisfy a given set of requirements.� A complete study of logic-circuit design is not one of our objectives, but� the methods we introduce will provide a good introduction to logic design.M04_WIDM0130_12_SE_C04.indd 1371/8/16 8:38 PM

138 Chapter 4/Combinational logiC CirCuits

A good portion of this chapter is devoted to the topic of troubleshooting this term has been adopted as a general description of the process of is�olat ing a problem or fault in any system and identifying a way of fixing it.� the analytical skills and efficient methods of troubleshooting are equally a�ppli cable to any system whether it is a plumbing problem, a problem with you�r car, a health issue, or a digital circuit. digital systems, implemented �using ttl-integrated circuits, have for decades provided an exceptional vehicl�e for the study of efficient, systematic troubleshooting methods. As with any �sys tem, the practical characteristics of the pieces that make up the system� must be understood in order to effectively analyze its normal operation, loca�te the trouble, and propose a remedy. we will present some basic characteristic�s and typical failure modes of logic ics in the ttl and cmOs families that� are still commonly used for laboratory instruction in introductory digital c�ourses and take advantage of this technology to teach some fundamental trouble shooting principles. in the last sections of this chapter, we will extend our knowledge of pr�o grammable logic devices and hardware description languages. the concept of programmable hardware connections will be reinforced, and we will pro� vide more details regarding the role of the development system. you will� learn the steps followed in the design and development of digital system�s today. enough information will be provided to allow you to choose the cor- rect types of data objects for use in simple projects to be presented la�ter in this text. Finally, several control structures will be explained, along with some instruction regarding their appropriate use. 4- 1 SUM-OF-

P R O DU CTS FORM

OUT CO MES Upon completion of this section, you will be able to: identify the form of a sum-of-products (sOp) expression. identify the form of a product-of-sums (pOs) expression. the methods of logic-circuit simplification and design that we will stud�y require the logic expression to be in a sum-of-products (SOP) form. some examples of this form are: 1. A BC�ABC

2. AB�ABC�C D�D

3.AB�CD�EF�GK�HL

each of these sum-of-products expressions consists of two or more And terms (products) that are Ored together. each And term consists of one� or more variables individually appearing in either complemented or uncomple mented form. For example, in the sum-of-products expression A BC�ABC,

the first And product contains the variables A , B, and C in their uncomple- mented (not inverted) form. the second And term contains A and C in their complemented (inverted) form. note that in a sum-of-products expressio�n, one inversion sign cannot cover more than one variable in a term (e.g., we cannot have A BC or RST).

Product-of-Sums

Another general form for logic expressions is sometimes used in logic-ci�rcuit design. called the product-of-sums (POS) form, it consists of two or more OrM04_WIDM0130_12_SE_C04.indd 1381/8/16 8:38 PM

sECTION 4-2/simplifying logiC CirCuits 139 terms (sums) that are Anded together. each Or term contains one or more variables in complemented or uncomplemented form. here are some product-of-sum expressions: 1. 1A�B�C21A�C2

2. 1A�B21C�D2F

3. 1 the methods of circuit simplification and design that we will be using are based on the sum-of-products form, so we will not be doing much with� the product-of-sums form. it will, however, occur from time to time in s�ome logic circuits that have a particular structure. OUTC O MEASSESSMENT

QUESTI

O NS 1. which of the following expressions is in sOp form? (a) AB�CD�E

(b) AB1C�D2

(c) 1A�B21C�D�F2

(d)MN�PQ

2. repeat question 1 for the pOs form. Upon completion of this section, you will be able to:Justify the use of simplification.

name two simplification techniques for digital circuits. Once the expression for a logic circuit has been obtained, we may be abl�e to reduce it to a simpler form containing fewer terms or fewer variables in� one or more terms. the new expression can then be used to implement a circuit that is equivalent to the original circuit but that contains fewer gates� and connections. to illustrate, the circuit of Figure 4-1(a) can be simplified to produce the

circuit of Figure 4-1(b). both circuits perform the same logic, so it should be

obvious that the simpler circuit is more desirable because it contains f�ewer A B BC (a) C x 5 A B C C A B C (b) A 1 BC x 5 A B(A 1 BC)FIGURE

4- 1 it is often possible to simplify a logic circuit such as that in part (a) to produce a more efficient implementation, shown in (b).M04_WIDM0130_12_SE_C04.indd 1391/8/16 8:38 PM

140 Chapter 4/Combinational logiC CirCuits

Outc O meAssessment

Questi

O ns 1.List two advantages of simplification.

2.List two methods of simplification.

4- 3 ALGEBRAI

CSIMPLIFICATION

OUT CO MES Apply Boolean algebra theorems and properties to reduce Boolean expressions.Manipulate expressions into POS or SOP form.

We can use the Boolean algebra theorems

that we studied in Chapter 3 to help us simplify the expression for a logic circuit. Unfortunately, it is not always obvious which theorems should be applied to produce the simplest result. Furthermore, there is no easy way to tell whether the simplified� expression is in its simplest form or whether it could have been simplif�ied further. Thus, algebraic simplification often becomes a process of trial and error. With experience, however, one can become adept at obtaining reaso�n ably good results. The examples that follow will illustrate many of the ways in which the Boolean theorems can be applied in trying to simplify an expression. You should notice that these examples contain two essential steps: 1.The original expression is put into SOP form by repeated application of DeMorgan's theorems and multiplication of terms.gates and will therefore be smaller and cheaper than the original. Furth�ermore, the circuit reliability will improve because there are fewer interconnec�tions that can be potential circuit faults.

Another strategic advantage of simplifying logic circuits involves the operational speed of circuits.Recall from previous discussions

that logic gates are subject to propagation delay. If practical logic circuits are config ured such that logical changes in the inputs must propagate through many� layers of gates in order to determine the output, they cannot possibly o�per ate as fast as circuits with fewer layers of gates. For example, compare� the circuits of Figure 4-1(a) and (b). In Figure

4-1(a), the longest path a signal

must travel involves three gates. In Figure 4-1(b), the longest signal path

(C) only involves two gates. Working toward a common form such as SOP � or POS assures similar propagation delay for all signals in the system and helps determine the maximum operating speed of the system. In subsequent sections, we will study two methods for simplifying logic � circuits. One method will utilize the Boolean algebra theorems and, as we shall see, is greatly dependent on inspiration and experience. The other� method (Karnaugh mapping) is a systematic, step-by-step approach. Some� instructors may wish to skip over this latter method because it is somew�hat mechanical and probably does not contribute to a better understanding of� Boolean algebra. This can be done without affecting the continuity or clarity of the rest of the text.M04_WIDM0130_12_SE_C04.indd 1401/8/16 8:38 PM

sECTION 4-3/algebraiC simplifiCation 141 solution The first step is to determine the expression for the output using the method presented in Section 3- 6 . The result is z�ABC+ABA C�

Once the expression is determined, it is usually a good idea to break do�wn all large inverter signs using DeMorgan's theorems and then multiply �out all terms. z�ABC+AB�A+C� [theorem (17)] �ABC+AB�A+C� [cancel double inversions] �ABC+ABA+ABC [multiply out] �ABC+AB+ABC [AA�A]

With the expression now in SOP form, we should look for common variables among the various terms with the intention of factoring. The first and third terms above have AC in common, which can be factored out: z�AC�B+B�+ABquotesdbs_dbs20.pdfusesText_26[PDF] logic translation generator

[PDF] logic translator

[PDF] logical and operators in c

[PDF] logical application architecture diagram example

[PDF] logical concurrency

[PDF] logical operator in c pdf

[PDF] logical operators in java

[PDF] logiciel pour apprendre le chinois

[PDF] logiciel pour apprendre le chinois gratuit

[PDF] logiciel pour apprendre le coran gratuit

[PDF] logiciel pour apprendre le russe gratuit

[PDF] logiciel pour apprendre le vocabulaire

[PDF] logiciel pour apprendre le vocabulaire français

[PDF] logik uottawa