TD systèmes logiques.pdf

TD systèmes logiques.pdf

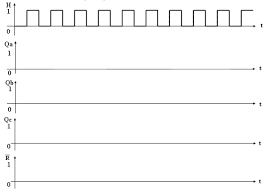

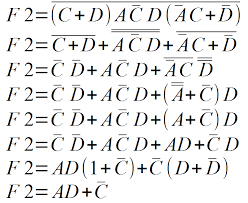

2) Simplifier les fonctions à l'aide de tableau de Karnaugh. 3) Dessiner le logigramme utilisant 3 portes NOR 1 porte NAND et une porte ET. Exercice 9: Une

Chapitre 2 : Algèbre de Boole

Chapitre 2 : Algèbre de Boole

C'est une méthode graphique basée sur la représentation des équations de sorties par des portes logiques. Cours et exercices corrigés" Technosup. N. Mansouri ...

Exercices corrigés (architecture ordinateurs et circuits logiques)

Exercices corrigés (architecture ordinateurs et circuits logiques)

Pour ce faire ajouter sur le dessin les résultats obtenus à la sortie de chacune des portes XOR du schéma. a) 0.

3 : Circuits logiques combinatoires

3 : Circuits logiques combinatoires

utilisant uniquement des portes NON-ET. a b. Exercice 3. On considère le schéma logique de la figure ci-

A.O. Partie 3 – circuits logiques

A.O. Partie 3 – circuits logiques

composé de portes logiques (e.g. porte ET

Architecture des Ordinateurs corrigé TD 4

Architecture des Ordinateurs corrigé TD 4

Exercice 1. Réalisation d'un additionneur/soustracteur (portes logiques disponibles : ET OU

1 Un peu de logique 2 Analyse de circuits logiques

1 Un peu de logique 2 Analyse de circuits logiques

TD 3 et 4 - Portes logiques et premiers circuits -. 1 Un peu de logique. Exercice 1.1. Exercice 1.2. R`egles de calcul. 1. Vérifier les lois de distributivité ...

RESUME DE COURS ET CAHIER DEXERCICES

RESUME DE COURS ET CAHIER DEXERCICES

Roux (Ediscience) très complet sur les circuits logiques de base y compris l'aspect technologique (TTL. CMOS…)

TD Electronique Appliquée.pdf

TD Electronique Appliquée.pdf

Exercice 4 : Corrigé. Exercice 5 : Corrigé. 1. Lorsque que Ve sera à 0 V IB = 0 portes logiques A et B du circuit ci-dessus ? 2) Calculer la période T

Recueil dexercices sur les propriétés des variables et fonctions

Recueil dexercices sur les propriétés des variables et fonctions

Donner les schémas logiques ou logigrammes de la fonction simplifiée utilisant : Page 5. 5. • logigramme 1 : des portes NON ET à partir de la forme simplifiée

1- Portes logiques et équations logiques

1- Portes logiques et équations logiques

EXERCICE : Soit le montage ci-dessous. a ) Déterminer l'équation logique de la fonction réalisée par ce montage. b ) Retrouver le résultat précédent en

Travaux dirigés de : Systèmes Logiques ( 1 ) & (2)

Travaux dirigés de : Systèmes Logiques ( 1 ) & (2)

portes logiques de base. Exercice 4: A partir du logigramme ci-contre. 1) Compléter la remarque suivante « La sortie S vaut.

Introduction aux circuits logiques de base

Introduction aux circuits logiques de base

Algèbre de Boole et les fonctions logiques sont On distingue les logiques positive et négative selon ... Composé uniquement de portes logiques OU.

Chapitre 3 ALGEBRE DE BOOLE Portes logiques de base

Chapitre 3 ALGEBRE DE BOOLE Portes logiques de base

https://fac.umc.edu.dz/ista/pdf/cours/chapitre%203_alg%C3%A8bre_de-boole.pdf

INF1500 : Logique des systèmes numériques

INF1500 : Logique des systèmes numériques

Convertir chaque circuit pour n'utiliser que des portes NON-ET ou bien NON-OU. Page 35. Sylvain Martel - INF1500. 35. Exercices. Convertir

Polytech Nice - PeiP1

Polytech Nice - PeiP1

EXERCICE I : Portes logiques à diodes (5.5 pts) à 1 V et le « 0 » logique à une tension inférieure à 1 V. I.1. Soit la porte logique ci-dessous ...

Architecture des Ordinateurs corrigé TD 1 Fonctions booléennes

Architecture des Ordinateurs corrigé TD 1 Fonctions booléennes

Exercice 4. Réalisation d'un additionneur/soustracteur (portes logiques disponibles : ET OU

Les systèmes logiques combinatoires 1. Exercice 1 : 2. Exercice 2

Les systèmes logiques combinatoires 1. Exercice 1 : 2. Exercice 2

Faire le logigramme des fonctions suivantes en utilisant que des portes logiques Pour le logigramme suivant donner l'équation logique de la sortie S en ...

A.O. Partie 3 – circuits logiques

A.O. Partie 3 – circuits logiques

http://www.phmartin.info/cours/ao/ (? TDs QCMs

1 Un peu de logique 2 Analyse de circuits logiques

1 Un peu de logique 2 Analyse de circuits logiques

Est-ce le minimum de portes nécessaire pour réaliser cette fonction? 6. Que fait ce circuit? 3 Réalisation de circuit. Exercice 3.1. `A partir des tables de

[PDF] TD systèmes logiquespdf - ISET Nabeul

[PDF] TD systèmes logiquespdf - ISET Nabeul

Algébrique des Fonctions Logiques Exercice 1: 1) Quelle propriété des fonctions logiques de base nous a permis de réaliser une porte logique

Portes logiques et algèbre de boole Exercices corrigés TP et Solutions

Portes logiques et algèbre de boole Exercices corrigés TP et Solutions

Exercices corrigés : Portes logiques et algèbre de boole SOLUTION EXERCICE 1 1) a b c La fonction logique réalisée est : le ET logique (AND)

[PDF] TD 3 et 4 - Portes logiques et premiers circuits - IGM

[PDF] TD 3 et 4 - Portes logiques et premiers circuits - IGM

TD 3 et 4 - Portes logiques et premiers circuits - 1 Un peu de logique Exercice 1 1 Remplir la table de vérité : a b a + b ab a + b ab a ? b 0 0 0 1

exercices corrigés sur les portes logiques pdf - F2School

exercices corrigés sur les portes logiques pdf - F2School

Étiquette exercices corrigés sur les portes logiques pdf Electronique Numérique : Cours et exercices corrigés · Electronique-Numérique-Cours-et-exercices-

[PDF] Association dopérateurs logiques

[PDF] Association dopérateurs logiques

Exemple : - Système de commande d'ouverture de la porte automatique d'un hôtel : EXERCICE : Soit le montage ci-dessous a ) Déterminer l'équation logique de la

[PDF] AO Partie 3 – circuits logiques

[PDF] AO Partie 3 – circuits logiques

Circuit logique: circuit (électronique/optique/ ) composé de portes logiques (e g porte ET OU ) et réalisant une ou plusieurs fonctions logiques; deux

portes logiques Examens Corriges PDF

portes logiques Examens Corriges PDF

Exercices corrigés (architecture ordinateurs et circuits logiques) A- Questions de culture générale (non corrigées ici) 1) Comment fonctionne le

[PDF] Les portes logiques - CoursTechInfo

[PDF] Les portes logiques - CoursTechInfo

1 Les portes logiques Nous avons jusqu'ici utilisé des boutons poussoirs et une lampe pour illustrer le fonctionnement des opérateurs logiques

[PDF] DS 2013-2014 No4 CORRECTIONpdf

[PDF] DS 2013-2014 No4 CORRECTIONpdf

EXERCICE II : Portes logiques (9pts) Dans cet exercice le « 1 » logique correspond à VDD et le « 0 » logique à 0 V (i e la masse) Une

Comment comprendre les portes logiques ?

La porte OR (OU) tire son nom du fait qu'elle se comporte comme l'opérateur logique inclusif OR (OU). La sortie a pour valeur « vrai » lorsqu'une entrée ou lorsque les deux entrées ont pour valeur « vrai ». Si les deux entrées ont pour valeur « faux », la sortie a pour valeur « faux ».Quelles sont les différentes portes logiques ?

Les portes logiques deux entrées

La porte logique AND (et) la porte logique AND, ou ET en Fran?is, porte bien sont nom car elle vas générer un '1' en sortie si et seulement si les deux bits en entrées sont égaux à '1'. La porte logique OR (ou) La porte logique XOR (ou exclusif) La porte logique NOR (non ou)OU exclusif 2 entrées ?

La fonction "OU Exclusif" est en principe d'une fonction de deux variables : S = A ? B La sortie est à 1 si une seule des deux entrées vaut 1, d'où son appellation « Ou exclusif ».- Cet opérateur est très utilisé en électronique, en informatique, et aussi en cryptographie du fait de ses propriétés intéressantes. Son symbole est traditionnellement un signe plus dans un cercle : « ? ».

Nom : Prénom : Groupe :

ECOLE POLYTECHNIQUE UNIVERSITAIRE DE NICE SOPHIA-ANTIPOLISCycle Initial Polytech

Première Année

Année scolaire 2013/2014

DS électronique

analogique No4 Note / 20 Mardi 13 Juin 2014 CORRECTION Durée : 1h30 Cours et documents non autorisés.

Calculatrice de type collège autorisée

Vous répondrez directement sur cette feuille. 7RXP pŃOMQJH HQPUH pPXGLMQPV JRPPH VP\OR UpSRQVHV" HVP LQPHUGLP Vous devez :

indiquer votre nom et votre prénom. éteindre votre téléphone portable ( 1 point par sonnerie).RAPPELS :

HPSpGMQŃH G·XQH ŃMSMŃLPp F : 1/(jC) [] HPSpGMQŃH G·XQH bobine L : jL []Quadripôle :

matrice impédance 2 1 22211211

2 1 I I.ZZ ZZ V V

2221212

2121111

I.ZI.ZV

I.ZI.ZV

Quadripôle :

matrice admittance 2 1 22211211

2 1 V V.YY YY I I

2221212

2121111

V.YV.YI

V.YV.YI

émetteur

collecteur baseP N+ N VBE VCE IC IE IBTransistor NPN

ibic vCE.ibRSvBE BC E ibic vCE.ibRSvBE BBCC EE Schéma électrique équivalent du transistor bipolaire NPN en régime de petit signal sans hoe 2EXERCICE I : Quadripôles (6 pts)

I.1. Par la méthode de votre choix,

déterminer les paramètres impédances de ce quadripôle : I1 V1V2R I2 RR I1 V1V2R I2 RR (0.25 pt) Z11 = 2R (0.25 pt) Z12 = R (0.25 pt) Z21 = R (0.25 pt) Z22 = 2RI.2. Par la méthode de votre choix,

déterminer les paramètres admittances de ce quadripôle : I1 V1V2 I2 L R C I1 V1V2 I2 L R C (0.25 pt) Y11 = jC+1/R (0.25 pt) Y12 = 1/R (0.25 pt) Y21 = 1/R (0.25 pt) Y22 = 1/R+1/jLIV.3. Par la méthode de votre choix,

déterminer les paramètres admittances de ce quadripôle : iB .iB hie I1 V1V2 I2 1/hoe REY11 = 1/RE + (1 + )/hie + hoe

Y12 = hoe

Y21 = /hie hoe

Y22 = hoe

I.5. Par la méthode de votre choix, déterminer 2 des4 paramètres impédances de ce quadripôle :

RR RR R RR RR I1I2 V1V2 R (0.5 pt) Z11 = 7R/2 (0.5 pt) Z12 = R 1 1 1 2 3I.6. Par la méthode de votre choix,

déterminer les paramètres impédances de ce quadripôle : I1 V1V2 I2 R RR R (0.25 pt) Z11 = (0.25 pt) Z12 = (0.25 pt) Z21 = (0.25 pt) Z22 =EXERCICE II : Portes logiques (9pts)

Dans cet exercice, le " 1 » logique correspond à VDD et le " 0 » logique à 0 V (i.e. la masse). Une

tension proche de VDD sera considérée comme un " 1 » et une tension proche de 0 V comme un" 0 ». Les diodes ont une résistance RS = 0 et une tension de seuil VS. Pour les transistors, il y a

aussi la tension de saturation VCEsat = 0. Les tensions de seuil des transistors et des diodes sont identiques. Pour des circuits logiques, les transistors fonctionnent en régimes bloqué et saturé. II.1. Soit la porte logique ci-dessous en technologie DL (Diode Logic). Compléter la table de vérité ci-contre. R1 D1 D2 VDD A B S A B S 0 0 0 0 1 0 1 0 0 1 1 1 1 0.5 4 II.2. Soit la porte logique ci-dessous en technologie DL (Diode Logic). Compléter la table de vérité ci-contre. R1 D1 D2 VDD A BS A B S 0 0 0 0 1 1 1 0 1 1 1 1 II.3. Soit la porte logique ci-dessous en technologie RTL (Resistor Transistor Logic). Compléter la table de vérité ci- contre. VDD S R1 A R2 B T1T2 A B S 0 0 1 0 1 0 1 0 0 1 1 0 0.5 1 5 II.4. Soit la porte logique ci-dessous en technologie RTL (Resistor Transistor Logic). Compléter la table de vérité ci- contre. R2 R1 VDD S R4 R3 VDD A B A B S 0 0 1 0 1 0 1 0 0 1 1 0 II.5. Soit la porte logique ci-dessous en technologie RTL (Resistor Transistor Logic). Compléter la table de vérité ci- contre. VDD S R1 AT1 R2 BT2 A B S 0 0 1 0 1 1 1 0 1 1 1 0 1 1 2 6 II.6. Soit la porte logique ci-dessous en technologie DTL (Diode Transistor Logic). Compléter la table de vérité ci- contre. R2R1 D1 D2 D3 VDD A B S A B S 0 0 1 0 1 1 1 0 1 1 1 0 II.7. Soit la porte logique ci-dessous en technologie TTL (Transistor Transistor Logic). Les diodes D1, D2 et D3 correspondent en fait à un transistor avec 2 émetteurs.Compléter la table de vérité ci-contre.

R2R1 D1 D2 D3 VDD A BS R4 R3 D4 T1 T2 T3 A B S 0 0 1 0 1 1 1 0 1 1 1 0 1 2 7 II.8. Soit la porte logique ci-dessous en technologie TTL7UMQVLVPRU 7UMQVLVPRU IRJLŃB FRPPH SRXU O·H[HUŃLŃH HHB7 OH

transistor T1 fonctionnent comme 2 diodes, idem pour le transistor T4. Compléter la table de vérité ci-contre. VDD R1 A R2 B R3 ST1T2T3T4

A B S 0 0 1 0 1 0 1 0 0 1 1 0 EXERCICE III : Petit amplificateur en classe A (5 pts)Soit le petit amplificateur en classe A

de la figure III.1. Les transistors ont un gain en courant , une tension de saturation VCEsat MLQVL TX·XQH résistance RS et une tension VS pour la diode base-émetteur. hoe sera négligée.On rappelle que le HP est constitué

G·XQH NRNLQH HP G·XQ aimant fixé à une membrane. D1 VDD RG VG EG RC HP T1 T2 VCE2Figure III.1

III.1. Quel est le rôle de D1 ?

A Faire jolie

B X GLVVLSHU O·pQHUJLH HPPMJMVLQpH GMQV OH +3 TXMQG 72 est bloqué C GLVVLSHU O·pQHUJLH GX JpQpUMPHXU (G dans le générateur VDDD GLVVLSHU O·pQHUJLH GH 71 dans T2

III.2. Dans quel régime se trouvent les transistors pour pouvoir amplifier le signal EG(t) ?A. Bloqué B. X Linéaire C. Saturé

0.5 2 0.5 8III.3. En vous aidant de OM PpPORGH GHV ŃUM\RQV GH ŃRXOHXU HP OM PpPORGH GH O·LQGH[ GRQQHU OH

schéma petit signal du circuit de la figure (III.1). La diode D1 étant forcement bloquée, il ne

faut pas la prendre en compte. Le HP sera considéré comme une résistance RHP. RG .ib1RSRC+ RHP

ib1 egVce2 B1C1Masse/VDD/E2

RSE1.ib2

ib2B2 C2 III.4. GpPHUPLQHU O·H[SUHVVLRQ GX JMLQ HQ PHQVLRQ que vous simplifierez en considérant >> 1 AV = g 2ce e v1bS1bSG

1bHPC1bS1bSG

2b1bHPC

i.1Ri.RR i.2.RR. i.1Ri.RR ii.RR. EE E E SG HPC2 RR RR E 2.5 2quotesdbs_dbs13.pdfusesText_19[PDF] fonctions logiques exercices corrigés

[PDF] calcul booléen en ligne

[PDF] calcul booléen bts sio

[PDF] exemple calcul capacité d'autofinancement

[PDF] calcul de la caf ? partir de l'ebe

[PDF] capacité d'autofinancement exercices corrigés maroc

[PDF] capacité d'autofinancement formule

[PDF] calcul caf méthode soustractive

[PDF] capacité d autofinancement formule de calcul

[PDF] calcul capacité d'autofinancement excel

[PDF] exercice cuisse abdos fessier

[PDF] vitesse du son en km/h

[PDF] protocole pour mesurer la vitesse du son

[PDF] formule vitesse du son