TD systèmes logiques.pdf

TD systèmes logiques.pdf

2) Simplifier les fonctions à l'aide de tableau de Karnaugh. 3) Dessiner le logigramme utilisant 3 portes NOR 1 porte NAND et une porte ET. Exercice 9: Une

Chapitre 2 : Algèbre de Boole

Chapitre 2 : Algèbre de Boole

C'est une méthode graphique basée sur la représentation des équations de sorties par des portes logiques. Cours et exercices corrigés" Technosup. N. Mansouri ...

Exercices corrigés (architecture ordinateurs et circuits logiques)

Exercices corrigés (architecture ordinateurs et circuits logiques)

Pour ce faire ajouter sur le dessin les résultats obtenus à la sortie de chacune des portes XOR du schéma. a) 0.

3 : Circuits logiques combinatoires

3 : Circuits logiques combinatoires

utilisant uniquement des portes NON-ET. a b. Exercice 3. On considère le schéma logique de la figure ci-

A.O. Partie 3 – circuits logiques

A.O. Partie 3 – circuits logiques

composé de portes logiques (e.g. porte ET

Architecture des Ordinateurs corrigé TD 4

Architecture des Ordinateurs corrigé TD 4

Exercice 1. Réalisation d'un additionneur/soustracteur (portes logiques disponibles : ET OU

1 Un peu de logique 2 Analyse de circuits logiques

1 Un peu de logique 2 Analyse de circuits logiques

TD 3 et 4 - Portes logiques et premiers circuits -. 1 Un peu de logique. Exercice 1.1. Exercice 1.2. R`egles de calcul. 1. Vérifier les lois de distributivité ...

RESUME DE COURS ET CAHIER DEXERCICES

RESUME DE COURS ET CAHIER DEXERCICES

Roux (Ediscience) très complet sur les circuits logiques de base y compris l'aspect technologique (TTL. CMOS…)

TD Electronique Appliquée.pdf

TD Electronique Appliquée.pdf

Exercice 4 : Corrigé. Exercice 5 : Corrigé. 1. Lorsque que Ve sera à 0 V IB = 0 portes logiques A et B du circuit ci-dessus ? 2) Calculer la période T

Recueil dexercices sur les propriétés des variables et fonctions

Recueil dexercices sur les propriétés des variables et fonctions

Donner les schémas logiques ou logigrammes de la fonction simplifiée utilisant : Page 5. 5. • logigramme 1 : des portes NON ET à partir de la forme simplifiée

1- Portes logiques et équations logiques

1- Portes logiques et équations logiques

EXERCICE : Soit le montage ci-dessous. a ) Déterminer l'équation logique de la fonction réalisée par ce montage. b ) Retrouver le résultat précédent en

Travaux dirigés de : Systèmes Logiques ( 1 ) & (2)

Travaux dirigés de : Systèmes Logiques ( 1 ) & (2)

portes logiques de base. Exercice 4: A partir du logigramme ci-contre. 1) Compléter la remarque suivante « La sortie S vaut.

Introduction aux circuits logiques de base

Introduction aux circuits logiques de base

Algèbre de Boole et les fonctions logiques sont On distingue les logiques positive et négative selon ... Composé uniquement de portes logiques OU.

Chapitre 3 ALGEBRE DE BOOLE Portes logiques de base

Chapitre 3 ALGEBRE DE BOOLE Portes logiques de base

https://fac.umc.edu.dz/ista/pdf/cours/chapitre%203_alg%C3%A8bre_de-boole.pdf

INF1500 : Logique des systèmes numériques

INF1500 : Logique des systèmes numériques

Convertir chaque circuit pour n'utiliser que des portes NON-ET ou bien NON-OU. Page 35. Sylvain Martel - INF1500. 35. Exercices. Convertir

Polytech Nice - PeiP1

Polytech Nice - PeiP1

EXERCICE I : Portes logiques à diodes (5.5 pts) à 1 V et le « 0 » logique à une tension inférieure à 1 V. I.1. Soit la porte logique ci-dessous ...

Architecture des Ordinateurs corrigé TD 1 Fonctions booléennes

Architecture des Ordinateurs corrigé TD 1 Fonctions booléennes

Exercice 4. Réalisation d'un additionneur/soustracteur (portes logiques disponibles : ET OU

Les systèmes logiques combinatoires 1. Exercice 1 : 2. Exercice 2

Les systèmes logiques combinatoires 1. Exercice 1 : 2. Exercice 2

Faire le logigramme des fonctions suivantes en utilisant que des portes logiques Pour le logigramme suivant donner l'équation logique de la sortie S en ...

A.O. Partie 3 – circuits logiques

A.O. Partie 3 – circuits logiques

http://www.phmartin.info/cours/ao/ (? TDs QCMs

1 Un peu de logique 2 Analyse de circuits logiques

1 Un peu de logique 2 Analyse de circuits logiques

Est-ce le minimum de portes nécessaire pour réaliser cette fonction? 6. Que fait ce circuit? 3 Réalisation de circuit. Exercice 3.1. `A partir des tables de

[PDF] TD systèmes logiquespdf - ISET Nabeul

[PDF] TD systèmes logiquespdf - ISET Nabeul

Algébrique des Fonctions Logiques Exercice 1: 1) Quelle propriété des fonctions logiques de base nous a permis de réaliser une porte logique

Portes logiques et algèbre de boole Exercices corrigés TP et Solutions

Portes logiques et algèbre de boole Exercices corrigés TP et Solutions

Exercices corrigés : Portes logiques et algèbre de boole SOLUTION EXERCICE 1 1) a b c La fonction logique réalisée est : le ET logique (AND)

[PDF] TD 3 et 4 - Portes logiques et premiers circuits - IGM

[PDF] TD 3 et 4 - Portes logiques et premiers circuits - IGM

TD 3 et 4 - Portes logiques et premiers circuits - 1 Un peu de logique Exercice 1 1 Remplir la table de vérité : a b a + b ab a + b ab a ? b 0 0 0 1

exercices corrigés sur les portes logiques pdf - F2School

exercices corrigés sur les portes logiques pdf - F2School

Étiquette exercices corrigés sur les portes logiques pdf Electronique Numérique : Cours et exercices corrigés · Electronique-Numérique-Cours-et-exercices-

[PDF] Association dopérateurs logiques

[PDF] Association dopérateurs logiques

Exemple : - Système de commande d'ouverture de la porte automatique d'un hôtel : EXERCICE : Soit le montage ci-dessous a ) Déterminer l'équation logique de la

[PDF] AO Partie 3 – circuits logiques

[PDF] AO Partie 3 – circuits logiques

Circuit logique: circuit (électronique/optique/ ) composé de portes logiques (e g porte ET OU ) et réalisant une ou plusieurs fonctions logiques; deux

portes logiques Examens Corriges PDF

portes logiques Examens Corriges PDF

Exercices corrigés (architecture ordinateurs et circuits logiques) A- Questions de culture générale (non corrigées ici) 1) Comment fonctionne le

[PDF] Les portes logiques - CoursTechInfo

[PDF] Les portes logiques - CoursTechInfo

1 Les portes logiques Nous avons jusqu'ici utilisé des boutons poussoirs et une lampe pour illustrer le fonctionnement des opérateurs logiques

[PDF] DS 2013-2014 No4 CORRECTIONpdf

[PDF] DS 2013-2014 No4 CORRECTIONpdf

EXERCICE II : Portes logiques (9pts) Dans cet exercice le « 1 » logique correspond à VDD et le « 0 » logique à 0 V (i e la masse) Une

Comment comprendre les portes logiques ?

La porte OR (OU) tire son nom du fait qu'elle se comporte comme l'opérateur logique inclusif OR (OU). La sortie a pour valeur « vrai » lorsqu'une entrée ou lorsque les deux entrées ont pour valeur « vrai ». Si les deux entrées ont pour valeur « faux », la sortie a pour valeur « faux ».Quelles sont les différentes portes logiques ?

Les portes logiques deux entrées

La porte logique AND (et) la porte logique AND, ou ET en Fran?is, porte bien sont nom car elle vas générer un '1' en sortie si et seulement si les deux bits en entrées sont égaux à '1'. La porte logique OR (ou) La porte logique XOR (ou exclusif) La porte logique NOR (non ou)OU exclusif 2 entrées ?

La fonction "OU Exclusif" est en principe d'une fonction de deux variables : S = A ? B La sortie est à 1 si une seule des deux entrées vaut 1, d'où son appellation « Ou exclusif ».- Cet opérateur est très utilisé en électronique, en informatique, et aussi en cryptographie du fait de ses propriétés intéressantes. Son symbole est traditionnellement un signe plus dans un cercle : « ? ».

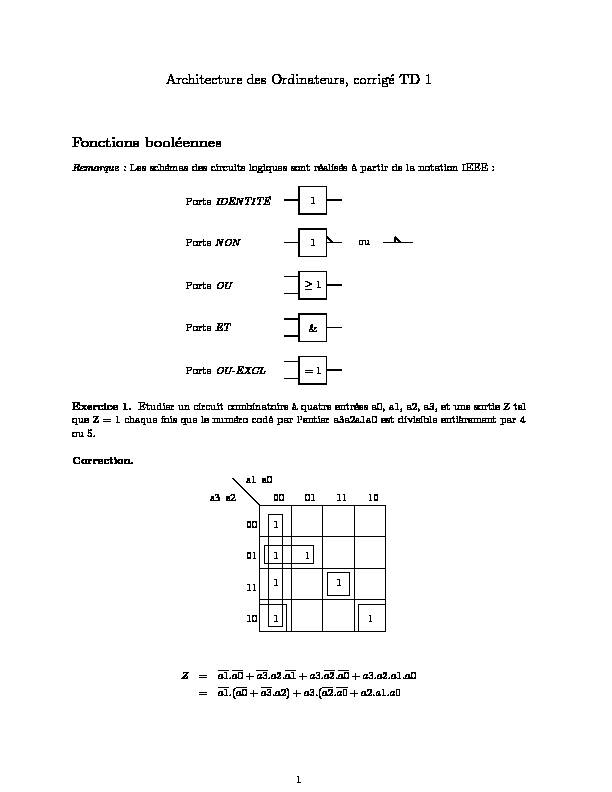

Architecture des Ordinateurs, corrig´e TD 1

Fonctions bool´eennes

Remarque :Les sch´emas des circuits logiques sont r´ealis´es `a partir de la notation IEEE :

PorteIDENTIT´E

1PorteNON1ou

PorteOU≥1

PorteET&

PorteOU-EXCL= 1

Exercice 1.Etudier un circuit combinatoire `a quatre entr´ees a0, a1, a2, a3, et une sortie Z telque Z = 1 chaque fois que le num´ero cod´e par l"entier a3a2a1a0 est divisible enti`erement par 4

ou 5.Correction.

00 01 11 10

00 01 1110a3 a2

a1 a0 1 111 11 11

Z=a1.a0 +a3.a2.a1 +a3.a2.a0 +a3.a2.a1.a0

a1.(a0 +a3.a2) +a3.(a2.a0 +a2.a1.a0 1 d"o`u le sch´ema : 1 1& 1 a3 a2 a1 a0 ZExercice 2.On consid`ere un ascenceur desservant un rez-de chauss´ee et trois ´etages. L"unit´e

logique de contrˆole de cet ascenceur re¸coit en entr´ee desrequˆetes de d´eplacement d"un ´etage vers

un autre, et g´en`ere en sortie les commandes correspondantes destin´ees au moteur de la cage. Il

s"agit de r´ealiser les circuits qui composent l"unit´e de contrˆole. Pour cela :- La valeur de l"´etage d"o`u part la requˆete (de 0 `a 3) est cod´ee par deux variables bool´eennes

x1 etx2. La valeur courante de l"´etage o`u se trouve la cage de l"ascenceur est cod´ee de fa¸con similaire par deux variables bool´eennesx3 etx4.- La sortie de l"unit´e de contrˆole est constitu´ee de troisfonctions bool´eennesHaut, Bas,

Stopdes quatre variables d"entr´eex1,x2,x3, etx4.Haut(x1,x2,x3,x4) est vraie quand la position courante de la cage estau-dessousde l"´etage d"o`u part la requˆete et fausse autrement. Inversement,Bas(x1,x2,x3,x4) est vraie quand la position courante de la cage estau-dessusde l"´etage d"o`u part la requˆete et fausse autrement. Finalement, Stop(x1,x2,x3,x4) est vraie quand l"´etage d"o`u part la requˆete et la position courante de l"ascenceur sont lesmˆemes,et fausse autrement.On vous demande de :

1. repr´esenter chacune des fonctions de l"unit´e de contrˆole par une table de Karnaugh;

2. simplifier ces fonctions;

3. dessiner les sch´emas des circuits correspondant `a chacune des fonctions simplifi´ees, en

utilisantle plus petit nombre possiblede portes.Correction.La valeur de l"´etage d"o`u part la requˆete est repr´esent´ee par la table binaire sui-

vante : x1x2Etage00Rez-de-chauss´ee

011er 102d113`eme

2De mˆeme, la valeur courante de l"´etage o`u se trouve la cagede l"ascenceur est repr´esent´e par la

table binaire : x3x4Etage00Rez-de-chauss´ee

011er 102d113`eme

Pour la fonction bool´eenneHaut(x1,x2,x3,x4)par exemple, il suffit de remplir une table deKarnaugh `a quatre variables de telle fa¸con que pour chaquecase un "1" y est plac´e si la valeur

courante de l"´etage o`u se trouve la cage de l"ascenceur estplus basse que la valeur de l"´etage d"o`u

part la requˆete, et un "0" y est plac´e sinon :00 01 11 10

00 01 11 10 x1 x2x3 x4 1 1 11110 0 0 0

000 0 0 0 L"expression bool´eenne r´esultante apr`es simplificationest :Haut(x1,x2,x3,x4) =x1.

x3 +x2.x3.x4 +x1.x2.x4 Bien que cette expression soit une forme normale disjonctive minimale, il est possible de pousser la simplification plus loin : x1. x3 +x2.x3.x4 +x1.x2.x4 =x1.x3 +x2.x4.(x3 +x1) Le circuit obtenu a exactement sept portes logiques : 1111 x1 x2 x3 x4&

Haut (x1, x2, x3, x4)

3 Les autres fonctions bool´eennes sont ´etablies de la mˆememani`ere.Exercice 3.On d´esire r´ealiser le syst`eme inclus dans une calculettequi `a un digit d´ecimal fait

correspondre l"allumage de segments repr´esentant ce digit. Le digit ´etant cod´e sur quatre valeurs

A,B,C,D,calculer les sept fonctionsa,b,c,d,e,f,gcommandant l"´eclairement des segments correspondants : gf e dcbaCorrection.ABCDabcdefg

00001111110

00010110000

00101101101

00111111001

01000110011

01011011011

01101011111

01111110000

10001111111

10011111011

1010xxxxxxx

1011xxxxxxx

1100xxxxxxx

1101xxxxxxx

1110xxxxxxx

1111xxxxxxx

1101 1 1

1 110X X X X00 01 11 10

00 01 1110A B

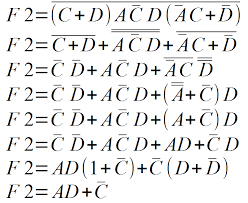

C D X X 4 a=A+C+B.D+B.D g=A+B.C+B.C+C.D

Exercice 4.R´ealisation d"un additionneur/soustracteur (portes logiques disponibles :ET,OU,NON,OU EXCL)

1. R´ealiser un demi-soustracteur (1 bitAavec 1 bitBsans retenue d"entr´ee) :

- Ecrire la table de v´erit´e. - Donner les ´equations de sortie. - Etablir le sch´ema logique.2. En comparant le circuit du demi-soustracteur avec celui d"un demi-additionneur, conce-

voir le plus simplement possible un circuit, appel´e demi-additionneur/soustracteur, qui `a partir d"un signal de commandeCet des entr´eesAetB, simule le demi-additionneur surAetBlorsque la commandeCest `a 0, et le demi-soustracteur surAetBlorsque la commandeCest `a 1 (suggestion : appliquer le signal de commande `a une des entr´ees d"une porteOU EXCL).3. A partir du demi-additionneur/soustracteur qui vient d"ˆetre r´ealis´e, concevoir un addi-

tionneur/soustracteur complet (1 bitAavec un bitBavec retenue d"entr´ee).quotesdbs_dbs2.pdfusesText_3[PDF] fonctions logiques exercices corrigés

[PDF] calcul booléen en ligne

[PDF] calcul booléen bts sio

[PDF] exemple calcul capacité d'autofinancement

[PDF] calcul de la caf ? partir de l'ebe

[PDF] capacité d'autofinancement exercices corrigés maroc

[PDF] capacité d'autofinancement formule

[PDF] calcul caf méthode soustractive

[PDF] capacité d autofinancement formule de calcul

[PDF] calcul capacité d'autofinancement excel

[PDF] exercice cuisse abdos fessier

[PDF] vitesse du son en km/h

[PDF] protocole pour mesurer la vitesse du son

[PDF] formule vitesse du son