Exercices de Révision sur les Circuits Combinatoires Multiplexeur

Exercices de Révision sur les Circuits Combinatoires Multiplexeur

Combinatoires Multiplexeur

Exercices corrigés sur les bascules rs pdf

Exercices corrigés sur les bascules rs pdf

exercices corrigés pdf algebre de boole

Logique combinatoire et multiplexage

Logique combinatoire et multiplexage

Donner le schéma du circuit. 5- Exercice 5 : (comparateur). Un comparateur n bits est un circuit logique contenant 2n entrées a0

Algèbre de Boole

Algèbre de Boole

Exercice. Trouver la forme simplifiée des fonctions à partir des deux tableaux ? Exercice 2 : Donner l'équation de F ? ... Multiplexeur / démultiplexeur.

Multiplexeurs et Dmultiplexeurs

Multiplexeurs et Dmultiplexeurs

schéma ci-dessous donne une image d'un multiplexeur 4 voies (E3 à E0) Le démultiplexeur est de ce fait souvent assimilé à un décodeur binaire décimal.

Introduction aux circuits logiques de base

Introduction aux circuits logiques de base

Principaux circuits MSI combinatoires. – Multiplexeur. – Démultiplexeur Le multiplexeur est un circuit combinatoire ... Le multiplexeur peut générer une.

VHDL - Logique programmable

VHDL - Logique programmable

Multiplexeur 4 vers 1 liste de conditions non exhaustive

Automatismes

Automatismes

1 – 11 Exercices . 2 – 3 Multiplexeur/ Démultiplexeur . ... 2 – 3 – 2 Démultiplexeur .

Logique combinatoire et séquentielle

Logique combinatoire et séquentielle

Le multiplexeur (sélecteur de données). Le décodeur-démultiplexeur . ... Exercice 3 Simplifier les fonctions logiques suivantes en utilisant la méthode ...

Exercices corrigés (architecture ordinateurs et circuits logiques)

Exercices corrigés (architecture ordinateurs et circuits logiques)

A- Questions de culture générale (non corrigées ici) multiplexeur sont numérotées de 0 à 3 de haut en bas (et le nombre ab est lu en binaire.

LCS 2016/2017

FEI-USTHB M.LICHOURI

Exercices de Révision sur les Circuits

Combinatoires, Multiplexeur, Démultiplexeur et

Circuit Séquentiel (Solution)

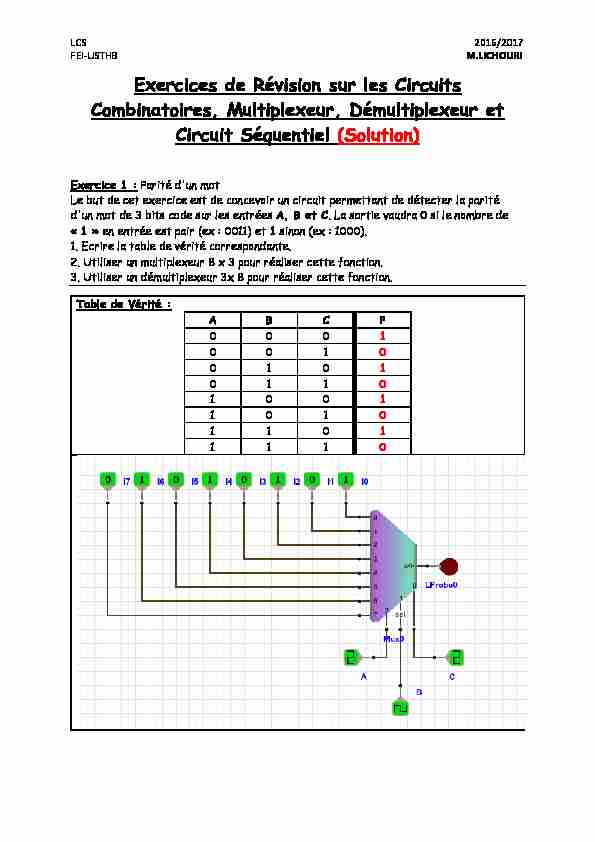

Exercice 1 : Parité d'un mot

Le but de cet exercice est de concevoir un circuit permettant de détecter la parité d'un mot de 3 bits code sur les entrées A, B et C. La sortie vaudra 0 si le nombre de " 1 » en entrée est pair (ex : 0011) et 1 sinon (ex : 1000).1. Ecrire la table de vérité correspondante.

2. Utiliser un multiplexeur 8 x 3 pour réaliser cette fonction.

3. Utiliser un démultiplexeur 3x 8 pour réaliser cette fonction.

Table de Vérité :

A B C P

0 0 0 1

0 0 1 0

0 1 0 1

0 1 1 0

1 0 0 1

1 0 1 0

1 1 0 1

1 1 1 0

LCS 2016/2017

FEI-USTHB M.LICHOURI

Exercice 2 : Incrémenteur

Une (grande) partie des additions effectuées par un ordinateur consistent simplement a ajouter 1 a une autre valeur x (on incrémente la valeur x).1. Réaliser un incrémenter 3 bit avec retenue de sortie (Entrées A0A1A2 ; Sorties

RI0I1I2).

2. Réaliser aussi le circuit d'un décrémenteur 3 bits, avec " 000 » cas indéfinis

(Entrées A0A1A2 ; Sorties D0D1D2).3. Réaliser la fonction D0 avec un 0X[ GH 3 HQPUpHV G·MGUHVVHs.

4. Réaliser la fonction D1 avec un G(0X[ GH 3 HQPUpHV G·MGUHVVHs.

5. Réaliser la fonction D2 avec un DEMux de 1x4 et un Mux 4x1.

Table de Vérité :

A0 A1 A2 R I0 I1 I2

0 0 0 0 0 0 1

0 0 1 0 0 1 0

0 1 0 0 0 1 1

0 1 1 0 1 0 0

1 0 0 0 1 0 1

1 0 1 0 1 1 0

1 1 0 0 1 1 1

1 1 1 1 0 0 0

Table de Vérité :

LCS 2016/2017

FEI-USTHB M.LICHOURI

A0 A1 A2 D0 D1 D2

0 0 0 0 0 0

0 0 1 0 0 0

0 1 0 0 0 1

0 1 1 0 1 0

1 0 0 0 1 1

1 0 1 1 0 0

1 1 0 1 0 1

1 1 1 1 1 0

LCS 2016/2017

FEI-USTHB M.LICHOURI

Exercice 3 : Rotation

On aime concevoir un circuit qui fait la rotation de 3 bit (CBA) à droite ou à gaucheVHORQ OM YMOHXU G·XQH YMULMNOH HQ HQPUpH GB

Ex : DCBA=0100 => D=0 (rotation à gauche) ; résultat (R0R1R2=001) DCBA=1100 => D=1 (rotation à droite) ; résultat (R0R1R2=010)1. Donner la table de vérité du circuit.

2. Donner les deux formes canoniques des sorties.

3. Réaliser les trois sorties avec des portes Nand ou Nor seulement.

LCS 2016/2017

FEI-USTHB M.LICHOURI

Exercice 4 :

Réaliser le circuit qui permet d'effectuer le complément à deux G·XQ QRPNUH NLQMLUH de3 bits j O·MLGH GH 3 Mux 8x1.

A B C M0 M1 M2

0 0 0 0 0 0

0 0 1 1 1 1

0 1 0 1 1 0

0 1 1 1 0 1

1 0 0 1 0 0

1 0 1 0 1 1

1 1 0 0 1 0

1 1 1 0 0 1

LCS 2016/2017

FEI-USTHB M.LICHOURI

Exercice 5 : Incrément de 5

Le code ROT5 permet de faire la rotation d'un nombre binaire en ajoutant 5 en binaire, sans retenue.Ex : ROT5(0000)=0101 ; ROT5(1111)=0100

Réaliser le circuit de conversion de binaire au ROT5 en utilisant un décodeur de 4 à 16 et 4 portes Or.LCS 2016/2017

FEI-USTHB M.LICHOURI

A B C D R0 R1 R2 R3

0 0 0 0 0 1 0 1

0 0 0 1 0 1 1 0

0 0 1 0 0 1 1 1

0 0 1 1 1 0 0 0

0 1 0 0 1 0 0 1

0 1 0 1 1 0 1 0

0 1 1 0 1 0 1 1

0 1 1 1 1 1 0 0

1 0 0 0 1 1 0 1

1 0 0 1 1 1 1 0

1 0 1 0 1 1 1 1

1 0 1 1 0 0 0 0

1 1 0 0 0 0 0 1

1 1 0 1 0 0 1 0

1 1 1 0 0 1 0 0

1 1 1 1 0 1 0 1

LCS 2016/2017

FEI-USTHB M.LICHOURI

Exercice 6 : Circuit Séquentiel

1. Trouvez la fonction Ft en fonction de A, B, C et D et Ft-1 à partir du circuit suivant.

2. Donnez la table de vérité réduite et éclaté de F pour C=D=1.

Si C=D=1 :

A B F 0 0 1 0 1 0 1 0 1 1 1 1LCS 2016/2017

FEI-USTHB M.LICHOURI

Exercice 7 :

En utilisant la table de transition de la bascule CD ; transformer la bascule CD enBascule RS.

Qn Qn+1 C D

0 0 0 x

0 1 x 1

1 0 0 1

1 1 1 0

Qn R S Qn+1 C D

0 0 0 0 0 x

0 0 1 1 x 1

0 1 0 0 0 x

0 1 1 x x x

1 0 0 1 1 0

1 0 1 1 1 0

1 1 0 0 0 1

1 1 1 x x x

quotesdbs_dbs2.pdfusesText_3[PDF] exercices corrigés nombres complexes math sup

[PDF] exercices corrigés nombres complexes mpsi pdf

[PDF] exercices corrigés nombres complexes terminale sti2d

[PDF] exercices corrigés nombres complexes type bac pdf

[PDF] exercices corrigés nombres réels mpsi

[PDF] exercices corrigés nombres réels pdf

[PDF] exercices corrigés nombres réels seconde

[PDF] exercices corrigés nomenclature 1ere s

[PDF] exercices corrigés nomenclature alcanes

[PDF] exercices corrigés nomenclature chimie organique terminale s

[PDF] exercices corrigés nomenclature terminale s

[PDF] exercices corrigés nomenclature ts

[PDF] exercices corrigés ondes progressives pdf

[PDF] exercices corrigés optique ondulatoire