Systèmes dExploitation - Gestion de la mémoire

Systèmes dExploitation - Gestion de la mémoire

d'Exploitation. Didier Verna. EPITA. Généralités. Allocation contigüe. Monoprogrammation. Multiprogrammation. Pagination. Segmentation. Pagination à plusieurs

610 Pagination - INF3173 Principes des systèmes dexploitation

610 Pagination - INF3173 Principes des systèmes dexploitation

610 Pagination. INF3173. Hiver 2021. 5 / 15. Page 6. Pagination pour le système d'exploitation. • Une table des pages par processus. • Le système d'exploitation.

Pagination (1/3) : la mémoire

Pagination (1/3) : la mémoire

La mémoire est une ressource de taille finie le système d'exploitation va en donner une représentation « logique »

Gestion de la mémoire

Gestion de la mémoire

principales à effectuer pour un système de pagination. Il existe également beaucoup d'autres considérations Syst`emes d'exploitation - Mırian Halfeld-Ferrari ...

Smart card introduction

Smart card introduction

Système d'exploitation. Gestion Mémoire. Licence Informatique. Jean-Louis Lanet • Dans le cas de systèmes de pagination à plusieurs niveaux l'utilisation ...

620 Mémoire virtuelle - INF3173 Principes des systèmes dexploitation

620 Mémoire virtuelle - INF3173 Principes des systèmes dexploitation

• Tout se fait côté système d'exploitation. Pagination cotée MMU (rappel). • La table des pages (MMU) indique seulement. • Si une page logique existe. • Et si

CHAPITRE IV : GESTION DE LA MEMOIRE

CHAPITRE IV : GESTION DE LA MEMOIRE

La mémoire physique est également subdivisée en blocs de la même. Page 7. Systèmes d'exploitation des Ordinateurs Dans un système de pagination à 2 niveaux ...

Unité 13: Systèmes dexploitation

Unité 13: Systèmes dexploitation

12.5.6 Pagination. Pour réaliser une mémoire virtuelle il faut avoir suffisamment de mémoire secondaire (disque) pour y stocker le programme tout entier et ses

Travaux Dirigés

Travaux Dirigés

et variable conditionnelle. • Dans un système de gestion mémoire virtuelle à pagination ... En conclusion le graphe est réduit de la des nœuds isolés.

Diapositive 1

Diapositive 1

28 апр. 2019 г. – Le système d'exploitation sélectionne un cadre de page peu utilisé ... Sur un système de pagination simple de 2¹ octets de mémoire. ⁶ octets.

Systèmes dExploitation - Gestion de la mémoire

Systèmes dExploitation - Gestion de la mémoire

Systèmes d'Exploitation. Didier Verna. EPITA. Généralités. Allocation contigüe. Monoprogrammation. Multiprogrammation. Pagination. Segmentation.

610 Pagination - INF3173 Principes des systèmes dexploitation

610 Pagination - INF3173 Principes des systèmes dexploitation

Un processus peut-il modifier la table des pages ? Jean Privat (UQAM). 610 Pagination. INF3173. Hiver 2021. 7 / 15

Gestion de la mémoire

Gestion de la mémoire

Syst`emes d'exploitation - M?rian Halfeld-Ferrari – p.1/71 Système de gestion de la mémoire (Memory manager): partie du SE qui gère la.

8 – PAGINATION MÉMOIRE

8 – PAGINATION MÉMOIRE

PAGINATION. Le principe de la pagination réside dans la division de la mémoire en zones de tailles performances du système on utilise un cache spécial

620 Mémoire virtuelle - INF3173 Principes des systèmes dexploitation

620 Mémoire virtuelle - INF3173 Principes des systèmes dexploitation

Tout se fait côté système d'exploitation. Pagination cotée MMU (rappel). • La table des pages (MMU) indique seulement. • Si une page logique existe.

Gestion de la mémoire

Gestion de la mémoire

Le gestionnaire de mémoire est un sous-ensemble du système d'exploitation. Son rôle est de Monoprogrammation sans va-et-vient ni pagination.

Pagination (1/3) : la mémoire

Pagination (1/3) : la mémoire

La mémoire est une ressource de taille finie le système d'exploitation va en donner une représentation « logique »

Systèmes dexploitation Unité 13

Systèmes dexploitation Unité 13

12.5.6 Pagination. L'adresse virtuelle est scindée en deux champs : Les derniers bits définissent un offset (adresse dans la page) le reste définit le numéro

Smart card introduction

Smart card introduction

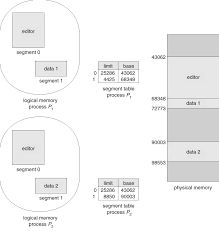

Système d'exploitation Comme pour la pagination la segmentation utilise un ... pagination

CHAPITRE IV : GESTION DE LA MEMOIRE

CHAPITRE IV : GESTION DE LA MEMOIRE

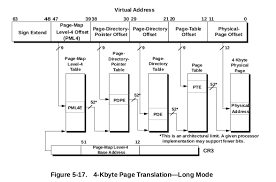

Systèmes d'exploitation des Ordinateurs. LOUKAM Mourad. 37. 4.4.4 Pagination multiniveaux : La plupart des SE modernes supportent un espace adresse logique

610 Pagination - INF3173 Principes des systèmes d'exploitation

610 Pagination - INF3173 Principes des systèmes d'exploitation

Pagination pour le système d’exploitation • Une table des pages par processus • Le système d’exploitation • Configureetmaintientchaquetabledespages • Positionnelatableduprocessusactiflorsdeschangementsde contextes Chez Linux • /proc/PID/pagemap (tableau binaire) pour chaque page logique

Différence entre la pagination et la - WayToLearnX

Différence entre la pagination et la - WayToLearnX

G La pagination 3 Conception des systèmes paginés Système paginé Le processeur essaie d’exécuter la première instruction processus lancé sans que leur page ne soit en mémoire Cela se produit plusieurs fois OS charge la page contenant cette instruction Puis le processeur dispose de la page et l’exécution se continue

Qu'est-ce que la pagination ?

La pagination est un système de gestion de mémoire. La pagination permet à un processus d’être stocké dans une mémoire de manière non contiguë. Stocker le processus d’une manière non-contiguë résout le problème de la fragmentation externe.

Quelle est la différence entre pagination et segmentation ?

Le matériel décide la taille de page. La taille du segment est spécifiée par l’utilisateur. La pagination implique une table de pages qui contient l’adresse de base de chaque page. La segmentation implique la table de segments qui contient le numéro de segment et le décalage (longueur du segment).

Quelle est la différence entre une page et un segment ?

Une page a une taille de bloc fixe. Un segment est de taille variable. La pagination peut entraîner une fragmentation interne. La segmentation peut conduire à une fragmentation externe. L’adresse spécifiée par l’utilisateur est divisée par le CPU en un numéro de page + un décalage.

Quels sont les systèmes informatiques d’organisation ?

Les systèmes informatiques d’organisation sont le plus souvent aujourd’hui des systèmes informatiques distribués (répartis), c’est-à-dire constitués par un assemblage d’éléments matériels et logiciels qui coopèrent pour réaliser un objectif commun en utilisant un réseau comme moyen d’échange des données.

Systèmes

d"ExploitationDidier Verna

EPITAGénéralités

Allocation

contigüeMonoprogrammation

Multiprogrammation

Pagination

SegmentationSystèmes d"Exploitation

Gestion de la mémoire

Didier Verna

didier@lrde.epita.fr http://www.lrde.epita.fr/˜didier 1/24Systèmes

d"ExploitationDidier Verna

EPITAGénéralités

Allocation

contigüeMonoprogrammation

Multiprogrammation

Pagination

SegmentationTable des matières

1Généralités2Allocation contigüeMonoprogrammation

Multiprogrammation

3Pagination4Segmentation2/24

Systèmes

d"ExploitationDidier Verna

EPITAGénéralités

Allocation

contigüeMonoprogrammation

Multiprogrammation

Pagination

SegmentationNiveaux d"adressage

Adresse symbolique: manipulée au niveau du

programmeAdresse logique: générée par le CPUAdresse physique: emplacement mémoire réelMMU(Memory Management Unit) : dispositif de liaison

d"adresse 4/24Systèmes

d"ExploitationDidier Verna

EPITAGénéralités

Allocation

contigüeMonoprogrammation

Multiprogrammation

Pagination

SegmentationLiaison d"adresse

Problème

IAdresses symboliques=)adresses physiques

IÀ quel moment fabriquer une adresse physique?Solutions ICompilation :" Code absolu »

Adresse de chargement connue.

Exemple :command.com.I

Chargement :" Code translatable »

Adressage relatif.I

Exécution :" Code dynamique »

L"emplacement du programme peut varier dans le

temps. Nécessite un matériel spécial. 5/24Systèmes

d"ExploitationDidier Verna

EPITAGénéralités

Allocation

contigüeMonoprogrammation

Multiprogrammation

Pagination

SegmentationTechniques de haut niveau

Recouvrements :(overlays) charger un processus partranches de code indépendantes. Niveau utilisateur.Chargement dynamique :charger le code nécessaire

uniquement quand on en a besoin. Niveau utilisateur.Édition de liens dynamique :bibliothèques partagées.Swapping: déplacement de processus entre mémoire et mémoire auxiliaire (disques). Coûteux en commutation. 6/24Systèmes

d"ExploitationDidier Verna

EPITAGénéralités

Allocation

contigüeMonoprogrammationMultiprogrammation

Pagination

SegmentationMonoprogrammation

Mainframes, Palm et systèmes embarqués, MS-DOSRAMRAMRAM RAM

ROM ROM

RAMUser Program

User Program

Operating SystemOperating System

Operating SystemDevice Drivers

0xFF..

0x00(BIOS)

8/24Systèmes

d"ExploitationDidier Verna

EPITAGénéralités

Allocation

contigüeMonoprogrammationMultiprogrammation

Pagination

SegmentationMultiprogrammation & partitions fixes

" OS/MFT » sur OS/360Operating SystemPartition 1Partition 2Partition 3Partition 4Operating System

Partition 1Partition 2Partition 3Partition 4

9/24Systèmes

d"ExploitationDidier Verna

EPITAGénéralités

Allocation

contigüeMonoprogrammationMultiprogrammation

Pagination

SegmentationLocalisation et protection

Modification du code :(OS/MFT, édition de liens) nécessite de connaître les mots à modifier. Ne résoudpas le problème de protection.=)Blocs de 2kB protégés par un code de 4 bits (PSW).Par MMU:(CDC 6600, Intel 8088)adresse

logiqueadresse physiqueDidier Verna

EPITAGénéralités

Allocation

contigüeMonoprogrammationMultiprogrammation

Pagination

SegmentationMultiprogrammation & partitions dynamiquesPrincipe

IUne partition mémoire par processus

IAllocation / libération de la mémoire en fonction de l"ordonnancementIIdem pour le swappingImplémentations

I Bitmap :1 bit par zone mémoire (kB) indiquant si la zone est libre ou occupée. Attention à la taille des zonesAvantages : simple, taille du bitmap connue

Inconvénients : lentI

Listes chaînées :zone libre / occupée, adresse de début et longueur. Tri par adresse, taille, listes distinctes de processus, trous. Listes doublement chaînées. 11/24Systèmes

d"ExploitationDidier Verna

EPITAGénéralités

Allocation

contigüeMonoprogrammationMultiprogrammation

Pagination

SegmentationPolitiques d"allocations

First-Fit :premier trou suffisant. Rapide.Next-Fit :idem, mais recherche à partir del"emplacement précédent. Un peu moins bon.Best-Fit :trou le plus petit possible. Moins performant.Worst-Fit :trou le plus grand. Bof.Quick-Fit :maintient de listes par tailles fréquentes.

Rapide pour la recherche, lent pour la désallocation.Remarque :attention aux politiques de tri des listes.12/24

Systèmes

d"ExploitationDidier Verna

EPITAGénéralités

Allocation

contigüeMonoprogrammationMultiprogrammation

Pagination

SegmentationFragmentation

Apparition de zones inoccupées dans la mémoireTypes IFragmentation externe: espace suffisant pour

l"allocation d"un nouveau processus, mais non contiguI Fragmentation interne: allocation volontaire de zones inoccupées pour diminuer le travail de gestion de la mémoireCompactage I Défragmentation de la mémoire par translation des processus (code dynamique) IStratégies de compactage difficiles à trouver, lenteur13/24Systèmes

d"ExploitationDidier Verna

EPITAGénéralités

Allocation

contigüeMonoprogrammation

MultiprogrammationPagination

SegmentationPagination

Allocation de zones de mémoire non contigües pour un même processusCadres de page: mémoire physique découpée en

zones de taille fixeAdresse logique: numéro de page + déplacement dans la pageTable de pages: liaison entre numéro de page et cadre de page (une table par processus)Taille des pages: puissance de 2 15/24Systèmes

d"ExploitationDidier Verna

EPITAGénéralités

Allocation

contigüeMonoprogrammation

MultiprogrammationPagination

SegmentationMMUpour la paginationpdmémoiref d

table de pagesadresse logiqueUCadresse

physique16/24Systèmes

d"ExploitationDidier Verna

EPITAGénéralités

Allocation

contigüeMonoprogrammation

MultiprogrammationPagination

SegmentationCaractéristiques

Pas de fragmentation externe, mais fragmentation

internePetites pages=)moins de fragmentationGrandes pages=)commutation moins coûteuseImpossible par définition d"accéder à une page interdite

Mécanismes de contrôle : pages (in)valides, en lecture, écriture, exécutionetc.Implémentation du partage de la mémoire plus facileTaille moyenne des pages : 2 - 4 Ko

17/24Systèmes

d"ExploitationDidier Verna

EPITAGénéralités

Allocation

contigüeMonoprogrammation

MultiprogrammationPagination

SegmentationSupport matériel

La pagination doit être rapide (ns)Registres dédiés :possible seulement pour des petites tables (ex. DEC PDP-11 : adresse 16 bits, pages de 8ko=)8 entrées).Mémoire principale :un unique registre " PTBR » (Page Table Base Register). Surcharge de commutation de contexte faible, mais temps d"accès double.Registres associatifs :" TLB» (Translation Look-Aside Buffers). Fonctionne comme un cache de la table de pages (ex. Motorola 68030 : TLBà 22 entrées, i486 : 32 entrées, taux de présence de 98%).I Gestion logicielle des TLB:par le système au lieu duMMU(Architectures RISC : Sparc, MIPS, Alpha).

Acceptable pour des TLBassez grands (64 entrées).Simplifie le MMU.18/24

Systèmes

d"ExploitationDidier Verna

EPITAGénéralités

Allocation

contigüeMonoprogrammation

MultiprogrammationPagination

SegmentationPagination à plusieurs niveaux

Exemple (courant) : adressage sur 32 bits + pages de 4 Ko. Une table de page contient alors 1 million d"entrées, soit 4Mo de mémoire!!À éviter

I allouer autant d"espace en contigu Icharger l"intégralité des tables de page en mémoirePagination de la table de page ISPARC: pagination 32 bits à trois niveaux

IMotorola 68030: pagination à quatre niveauxProblème: trois ou quatre indirections à chaque fois

que l"on doit récupérer un octet. 19/24Systèmes

d"ExploitationDidier Verna

EPITAGénéralités

Allocation

contigüeMonoprogrammation

MultiprogrammationPagination

SegmentationTable de pages inversée

Autre solution au problème de la taille des tables de pagesPrincipe I Une unique table de pages pour tout le système, indexée par les cadres de page IChaque entrée contient un numéro de processus et un numéro de page virtuelleProblèmes I Liaison d"adresse plus compliquée (parcours de la table).=)TLB, tables de hash par adresse virtuelle. IPartage de pages plus difficile à implémenter au niveau système.Utilisation actuelle: IBM, HP, de plus en plus d"architectures 64 bits. 20/24Systèmes

d"ExploitationDidier Verna

EPITAGénéralités

Allocation

contigüeMonoprogrammation

Multiprogrammation

PaginationSegmentationSegmentation

Segmentationvs.Pagination

I Pagination :obtenir un espace d"adresselinéaireaussi grand que souhaité.=)Dimension 1 ISegmentation :obtenirplusieursespaces d"adressage distincts (segments).=)Dimension 2 (ex. compilateur + pile, source, table de symboles, ASTetc.)Principe ISegment = unitélogique(niveau utilisateur)

ITaille variable, mais indépendante des autres segments IFacilité de partage (ex. bibliothèques partagées) IFacilité de protection (ex. lecture, écriture. exécution)Implémentation I Table de segments :idée analogue à la paginationIAdresse logique: nom du segment + déplacement

ISegmentation et pagination combinée22/24

Systèmes

d"ExploitationDidier Verna

EPITAGénéralités

Allocation

contigüeMonoprogrammation

Multiprogrammation

PaginationSegmentationSegmentation et Pagination

Exemple : Intel Pentium16K segments de 4 Go par processus, dont : I8K segments privés (une table de descripteurs locale " LDT » par processus) I8K segments partageables (une table de descripteurs globale " GDT)Sélecteur de segment (16 bits) + offset (32 bits)=) " Adresse linéaire » (32 bits)Base Address LimitOther fieldsDescriptor

+RingG/L DTIndex113 2Offset32

32 bits linear address

23/24Systèmes

d"ExploitationDidier Verna

EPITAGénéralités

Allocation

contigüeMonoprogrammation

Multiprogrammation

PaginationSegmentationIntel Pentium (suite)

Pagination :Pagination à 2 niveaux.

Pages de 4Ko.Directory Page Offset10 10 12Protection :4 anneaux différents.

Progression en

profondeur par portes / guichets. 2103Syscalls

DLLsUserland

Kernel

24/24quotesdbs_dbs8.pdfusesText_14

[PDF] larousse conjugaison pdf

[PDF] telecharger larousse difficultés grammaticales pdf

[PDF] larousse grammaire francais

[PDF] larousse orthographe pdf

[PDF] larousse livre de bord orthographe pdf

[PDF] introduction grammaire generative

[PDF] chomsky théorie

[PDF] chomsky linguistique pdf

[PDF] aspects de la théorie syntaxique pdf

[PDF] grammaire grecque ancien

[PDF] sommaire paginé word

[PDF] sommaire paginé rapport de stage

[PDF] grammaire grec moderne pdf

[PDF] cours word 2007 gratuit