Systèmes dExploitation - Gestion de la mémoire

Systèmes dExploitation - Gestion de la mémoire

d'Exploitation. Didier Verna. EPITA. Généralités. Allocation contigüe. Monoprogrammation. Multiprogrammation. Pagination. Segmentation. Pagination à plusieurs

610 Pagination - INF3173 Principes des systèmes dexploitation

610 Pagination - INF3173 Principes des systèmes dexploitation

610 Pagination. INF3173. Hiver 2021. 5 / 15. Page 6. Pagination pour le système d'exploitation. • Une table des pages par processus. • Le système d'exploitation.

Pagination (1/3) : la mémoire

Pagination (1/3) : la mémoire

La mémoire est une ressource de taille finie le système d'exploitation va en donner une représentation « logique »

Gestion de la mémoire

Gestion de la mémoire

principales à effectuer pour un système de pagination. Il existe également beaucoup d'autres considérations Syst`emes d'exploitation - Mırian Halfeld-Ferrari ...

Smart card introduction

Smart card introduction

Système d'exploitation. Gestion Mémoire. Licence Informatique. Jean-Louis Lanet • Dans le cas de systèmes de pagination à plusieurs niveaux l'utilisation ...

620 Mémoire virtuelle - INF3173 Principes des systèmes dexploitation

620 Mémoire virtuelle - INF3173 Principes des systèmes dexploitation

• Tout se fait côté système d'exploitation. Pagination cotée MMU (rappel). • La table des pages (MMU) indique seulement. • Si une page logique existe. • Et si

CHAPITRE IV : GESTION DE LA MEMOIRE

CHAPITRE IV : GESTION DE LA MEMOIRE

La mémoire physique est également subdivisée en blocs de la même. Page 7. Systèmes d'exploitation des Ordinateurs Dans un système de pagination à 2 niveaux ...

Unité 13: Systèmes dexploitation

Unité 13: Systèmes dexploitation

12.5.6 Pagination. Pour réaliser une mémoire virtuelle il faut avoir suffisamment de mémoire secondaire (disque) pour y stocker le programme tout entier et ses

Travaux Dirigés

Travaux Dirigés

et variable conditionnelle. • Dans un système de gestion mémoire virtuelle à pagination ... En conclusion le graphe est réduit de la des nœuds isolés.

Diapositive 1

Diapositive 1

28 апр. 2019 г. – Le système d'exploitation sélectionne un cadre de page peu utilisé ... Sur un système de pagination simple de 2¹ octets de mémoire. ⁶ octets.

Systèmes dExploitation - Gestion de la mémoire

Systèmes dExploitation - Gestion de la mémoire

Systèmes d'Exploitation. Didier Verna. EPITA. Généralités. Allocation contigüe. Monoprogrammation. Multiprogrammation. Pagination. Segmentation.

610 Pagination - INF3173 Principes des systèmes dexploitation

610 Pagination - INF3173 Principes des systèmes dexploitation

Un processus peut-il modifier la table des pages ? Jean Privat (UQAM). 610 Pagination. INF3173. Hiver 2021. 7 / 15

Gestion de la mémoire

Gestion de la mémoire

Syst`emes d'exploitation - M?rian Halfeld-Ferrari – p.1/71 Système de gestion de la mémoire (Memory manager): partie du SE qui gère la.

8 – PAGINATION MÉMOIRE

8 – PAGINATION MÉMOIRE

PAGINATION. Le principe de la pagination réside dans la division de la mémoire en zones de tailles performances du système on utilise un cache spécial

620 Mémoire virtuelle - INF3173 Principes des systèmes dexploitation

620 Mémoire virtuelle - INF3173 Principes des systèmes dexploitation

Tout se fait côté système d'exploitation. Pagination cotée MMU (rappel). • La table des pages (MMU) indique seulement. • Si une page logique existe.

Gestion de la mémoire

Gestion de la mémoire

Le gestionnaire de mémoire est un sous-ensemble du système d'exploitation. Son rôle est de Monoprogrammation sans va-et-vient ni pagination.

Pagination (1/3) : la mémoire

Pagination (1/3) : la mémoire

La mémoire est une ressource de taille finie le système d'exploitation va en donner une représentation « logique »

Systèmes dexploitation Unité 13

Systèmes dexploitation Unité 13

12.5.6 Pagination. L'adresse virtuelle est scindée en deux champs : Les derniers bits définissent un offset (adresse dans la page) le reste définit le numéro

Smart card introduction

Smart card introduction

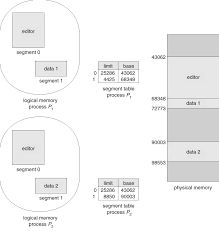

Système d'exploitation Comme pour la pagination la segmentation utilise un ... pagination

CHAPITRE IV : GESTION DE LA MEMOIRE

CHAPITRE IV : GESTION DE LA MEMOIRE

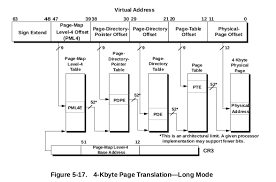

Systèmes d'exploitation des Ordinateurs. LOUKAM Mourad. 37. 4.4.4 Pagination multiniveaux : La plupart des SE modernes supportent un espace adresse logique

610 Pagination - INF3173 Principes des systèmes d'exploitation

610 Pagination - INF3173 Principes des systèmes d'exploitation

Pagination pour le système d’exploitation • Une table des pages par processus • Le système d’exploitation • Configureetmaintientchaquetabledespages • Positionnelatableduprocessusactiflorsdeschangementsde contextes Chez Linux • /proc/PID/pagemap (tableau binaire) pour chaque page logique

Différence entre la pagination et la - WayToLearnX

Différence entre la pagination et la - WayToLearnX

G La pagination 3 Conception des systèmes paginés Système paginé Le processeur essaie d’exécuter la première instruction processus lancé sans que leur page ne soit en mémoire Cela se produit plusieurs fois OS charge la page contenant cette instruction Puis le processeur dispose de la page et l’exécution se continue

Qu'est-ce que la pagination ?

La pagination est un système de gestion de mémoire. La pagination permet à un processus d’être stocké dans une mémoire de manière non contiguë. Stocker le processus d’une manière non-contiguë résout le problème de la fragmentation externe.

Quelle est la différence entre pagination et segmentation ?

Le matériel décide la taille de page. La taille du segment est spécifiée par l’utilisateur. La pagination implique une table de pages qui contient l’adresse de base de chaque page. La segmentation implique la table de segments qui contient le numéro de segment et le décalage (longueur du segment).

Quelle est la différence entre une page et un segment ?

Une page a une taille de bloc fixe. Un segment est de taille variable. La pagination peut entraîner une fragmentation interne. La segmentation peut conduire à une fragmentation externe. L’adresse spécifiée par l’utilisateur est divisée par le CPU en un numéro de page + un décalage.

Quels sont les systèmes informatiques d’organisation ?

Les systèmes informatiques d’organisation sont le plus souvent aujourd’hui des systèmes informatiques distribués (répartis), c’est-à-dire constitués par un assemblage d’éléments matériels et logiciels qui coopèrent pour réaliser un objectif commun en utilisant un réseau comme moyen d’échange des données.

TD 8 Mémoire8 - PAGINATION M

ÉMOIRE

1.PAGINATION

Le principe de la pagination r

éside dans la division de la mémoire en zones de tailles fixes appel ées "pages". L'espace de travail d'un processus est divisé en pages. Quand le processus est exécuté, seules les pages dont il a besoin sont chargées en mémoire centrale.On dispose d'une machine monoprocesseur, ayant une m

émoire centrale de 32K mots, une

page faisant 512 mots (64 pages en m émoire centrale), un bloc (unité de stockage sur le disque) faisant 512 mots. On consid ère le programme suivant :AdresseInstructionSignificationELoadx Nreg d'index X = N

Load S,Xreg accumulateur A = S[X]

Add VA = A + V

Store T,XT[X] = A

Subx KX = X K

Brxpz E + 1Si X >= 0 alors aller en E + 1

Stop Où:•X est un registre d'index,

•A est un registre accumulateur, •E est l'adresse du d ébut du programme : 512 * 1 + 508, •S et T sont des tableaux de taille [0 .. N], S [0]étant à l'adresse 512 * 11 + 168 et T[0]

se trouvant à l'adresse 512 * 12 +456, •N est une constante égale à 799 se trouvant à l'adresse 512 * 6 + 500, •V est une constante égale à 2 se trouvant à l'adresse 512 * 8 + 100, •K est une constante égale à 2 se trouvant à l'adresse 512 * 8 + 10. Ce programme effectue la chose suivante : x = N; do {T[X] = S[X] + V;

x -= K; } while (x >= 0);En fin d'ex

écution, les pages modifiées sont recopiées en mémoire secondaire.1.1. Sachant que chaque instruction, constante ou variable simple occupe un mot mémoire,

repr ésenter l'espace d'adressage du processus (numéro de page / déplacement dans la page de chaque donnée). Quels droits doiton affecter aux différentes pages du processus ?Les actions de gestion de la m

émoire peuvent être représentées à l'aide des opérations suivantes :TD 8 MémoireTrap (p) : D

éfaut de page pour la page p.Charg (p,c) :Chargement de la page p dans la case c en mémoire centrale.Dech (p,c) : D

échargement de la page p se trouvant à la place c en mémoire centrale.Mod (p,c,d) : Modification de la table des pages, p : num

éro de page du processus, c

place en m émoire centrale, d droits d'accès de la page.Le processus pr écédent dispose pour s'exécuter des pages de mémoire centrale 17, 21, 22,23, 37 et 42.

1.2.En utilisant un algorithme premier charg

é/premier déchargé et en supposant qu'au départ, aucune page n'est charg ée, décrire les actions de gestion de mémoire sous la forme d'une suite compos ée des opérations précédentes. Donner la table des pages finale.2.SEGMENTATION PAGINÉEOn consid

ère une mémoire segmentée paginée. La taille des pages est de 512 mots.Le processus P poss

ède 3 segments : le segment 0 pour le code, le segment 1 pour la pile et le segment 2 pour les donn ées. Le segment 0 a 1500 mots, le segment 1 en a 2000 et le segment 2 en a 3000. On suppose que la table des segments et les tables de pages sont déjà

chargées en mémoire.2.1.

Quels sont les droits associ

és à chaque segment ? Quel est l'avantage de découper ainsi l'espace d'adressage du processus ?Seules les pages suivantes ont

été chargées (on donne le doubletDans quelle case m

émoire est chargée la page <0, 0> ?

2.3. D écrire brièvement ce qui se passe sur une tentative de lecture en <0 : 1678>, <1 : 567> et <2 : 1600> (Ces adresses sont au format segmenté).2.4.

Conna îton l'adresse physique de la variable d'adresse virtuelle <1 : 1060> ? Si oui, quelle estelle ? Sinon, justifiez.3. CACHE ET M

ÉMOIRE VIRTUELLE

Avec une m

émoire paginée, l'accès à une donnée nécessite deux accès à la mémoire : un

pour lire la table des pages, l'autre pour lire la donnée. Pour ne pas diviser par deux les

performances du syst ème, on utilise un cache spécial, appelé TLB (Translation Lookaside TD 8 MémoireBuffers), qui permet de stocker le coupleées. 3.1.

On suppose qu'un acc

ès à la TLB demande 20 ns et qu'un accès mémoire demande 100 ns. Pour une TLB avec un taux de hit de 90%, quel est le temps moyen d'accès à une donnée ?

En plus de la TLB qui permet une translation rapide de l'adresse logiqueà l'adresse

physique, le syst ème dispose d'un cache pour améliorer la vitesse d'accès aux données. Le cache est une m émoire à accès rapide, structurée en lignes. Chaque ligne stocke un bloc de donn ées d'une part, tout ou partie de l'adresse du bloc permettant d'identifier le bloc de façon unique, ainsi que diverses informations relatives à la validité, l'ancienneté, ... dudit

bloc.La combinaison de la m

émoire cache et de la mémoire virtuelle est délicate : ou bien le cache contient les adresses physiques des blocs, et dans ces conditions la traduction adresse virtuelle adresse physique doit être faite entre le processeur et le cache; ou bien le cache contient les adresses virtuelles des blocs, et la traduction adresse virtuelleadresse physique a lieu entre le cache et la mémoire.3.2.

Repr ésentez schématiquement l'organisation de la hiérarchie mémoire dans les deux cas.Quels sont les avantages et inconv

énients de chaque organisation ?

quotesdbs_dbs44.pdfusesText_44[PDF] larousse conjugaison pdf

[PDF] telecharger larousse difficultés grammaticales pdf

[PDF] larousse grammaire francais

[PDF] larousse orthographe pdf

[PDF] larousse livre de bord orthographe pdf

[PDF] introduction grammaire generative

[PDF] chomsky théorie

[PDF] chomsky linguistique pdf

[PDF] aspects de la théorie syntaxique pdf

[PDF] grammaire grecque ancien

[PDF] sommaire paginé word

[PDF] sommaire paginé rapport de stage

[PDF] grammaire grec moderne pdf

[PDF] cours word 2007 gratuit