Les portes logiques

Les portes logiques

Combinaisons de portes logiques. Ces trois fonctions logiques de base peuvent être combinées pour réaliser des opérations plus élaborées en interconnectant les

Les portes logiques en mode interactif dans Proteus

Les portes logiques en mode interactif dans Proteus

L'objectif de ce TP est de maîtriser le logiciel ISIS Proteus 7 Professional en mode interactif afin de créer de tester et de valider des logigrammes d'une

TD systèmes logiques.pdf

TD systèmes logiques.pdf

1) Quelle propriété des fonctions logiques de base nous a permis de réaliser une porte logique portes NOR 1 porte NAND et une porte ET. Exercice 9: Une ...

CMOS et portes logiques

CMOS et portes logiques

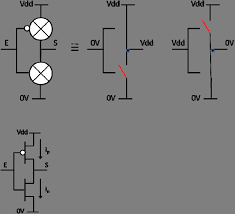

2 REALISATION DES PORTES LOGIQUES. 2.1 L'inverseur CMOS statique. La logique CMOS utilise les deux types de transistors. La Figure 2 modélise le.

Transistor Portes Logiques et Circuits Combinatoires

Transistor Portes Logiques et Circuits Combinatoires

20 avr. 2020 Portes logiques. Circuits combinatoires. Conclusion. Porte NON. La porte logique la plus simple est celle qui réalise une inversion logique.

Introduction aux circuits logiques de base

Introduction aux circuits logiques de base

Analyse de circuit logique. • 3 entrées 1 sortie. • Composé uniquement de portes logiques OU

COMPILATION De lalgorithme à la porte logique

COMPILATION De lalgorithme à la porte logique

3 janv. 2023 De l'algorithme à la porte logique. Télécom SudParis. CSC4251-4252. Pascal Hennequin. Page 2. 03/01/2023. 2 / 127. Sommaire (1/2). Introduction.

Câblage des portes logiques - O Mise en situation et objectifs du TP G

Câblage des portes logiques - O Mise en situation et objectifs du TP G

Q Comment réaliser un logigramme réel en utilisant des portes logiques électroniques. Q Comment sont représentés le 0 logique et le 1 logique dans un montage

Compilation : De lalgorithme à la porte logique

Compilation : De lalgorithme à la porte logique

- De la porte logique au processeur. - Instructions registres

Câblage des portes logiques

Câblage des portes logiques

Q Comment réaliser un logigramme réel en utilisant des portes logiques électroniques. Q Comment sont représentés le 0 logique et le 1 logique dans un montage

Les portes logiques

Les portes logiques

effectuées par des portes logiques. Ce sont des circuits qui combinent les signaux logiques présentés à leurs entrées sous forme de tensions.

04-Les-portes-logiques.pdf

04-Les-portes-logiques.pdf

LES PORTES LOGIQUES. Le fonctionnement des ordinateurs tout comme d'autres appareils électroniques repose sur l'emploi des circuits électroniques de logique.

Les portes logiques en mode interactif dans Proteus

Les portes logiques en mode interactif dans Proteus

II – 1 – Réalisez dans Proteus le Montage 1 utilisant une porte logique ET 4081.IEC deux générateurs logiques LOGICSTATE en entrée et une sonde logique.

GELE5340 - Chapitre 5

GELE5340 - Chapitre 5

Une porte logique en CMOS complémentaire est une combinaison de deux réseaux de On peut créer quelques r`egles pour la construction des portes logiques.

Introduction aux circuits logiques de base

Introduction aux circuits logiques de base

Toute fonction logique peut être réalisée à l'aide d'un nombre de fonctions logiques de base appelées portes. • Un circuit se représente par un logigramme.

Chapitre 3 - Principes de la logique combinatoire

Chapitre 3 - Principes de la logique combinatoire

Trois autres portes logiques sont fréquemment utilisées : la porte NAND (NON-ET) la porte NOR (NON-OU) et la porte XOR (Exclusivement-OU). Ces portes

VHDL – Logique programmable

VHDL – Logique programmable

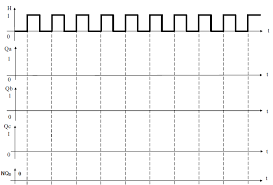

Description d'une porte logique AND en SystemC . Logique combinatoire : portes logiques traditionnelles AND et OR. • Logique séquentielle : flip-flops.

symboles des portes logiques.pdf

symboles des portes logiques.pdf

IUT de Nancy-Brabois http://perso.orange.fr/fabrice.sincere. SYMBOLES DES PORTES LOGIQUES. Fonction logique Symbole européen. Symbole américain.

Chapitre 3 ALGEBRE DE BOOLE Portes logiques de base

Chapitre 3 ALGEBRE DE BOOLE Portes logiques de base

https://fac.umc.edu.dz/ista/pdf/cours/chapitre%203_alg%C3%A8bre_de-boole.pdf

Porte logique

Porte logique

Présentation du module Porte logique. Porte logique. Ce module permet d'utiliser les fonctions logiques de base : - ET. - OU. - NON ET. - NON OU.

Les portes logiques - Cours Tech Info

Les portes logiques - Cours Tech Info

Les portes logiques Nous avons jusqu’ici utilisé des boutons poussoirs et une lampe pour illustrer le fonctionnement des opérateurs logiques En électronique digitale les opérations logiques sont effectuées par des portes logiques Ce sont des circuits qui combinent les signaux logiques

Les portes et fonctions logiques - Codeur Pro

Les portes et fonctions logiques - Codeur Pro

La fonction logique d’un élément combinatoire est l’opération réalisée par celui-ci Elle peut être dé?nie par des équations ou des tables de vérité Ici la table de vérité utilisée pour les précédents chronogrammes:

Les portes logiques - Prof-TC

Les portes logiques - Prof-TC

On peut définir chaque porte logique par son symbole sa table de vérité (qui a pour rôle de montrer la correspondance entre la sortie et toutes les combinaisons de valeurs que peuvent prendre la ou les entrées) Mais également son équivalence en schéma électrique

Cours de Systèmes Logiques 1 - Portes logiques - HEIG-VD

Cours de Systèmes Logiques 1 - Portes logiques - HEIG-VD

E Messerli Y Thoma (HES-SO / HEIG-VD / REDS) Portes logiques Septembre 2019 21 / 58 Modèles logiques Les portes logiques de base Etude des fonctions d’une variable : Nous verrons la porte logique de base : NON Etude des fonctions de deux variables : Nous verrons les portes logiques de base : ET OU Nous verrons ensuite des combinaisons

CHAPITRE 3 LES CIRCUITS LOGIQUES - uqacca

CHAPITRE 3 LES CIRCUITS LOGIQUES - uqacca

Pour représenter la porte OU dans les circuits on utilise le symbole suivant: Figure 3 : Porte OU Symbole a b a + b ( a U b ) Bien sûr la boîte noire qui porte le nom OU dans le schéma ne décrit pas le circuit électronique approprié pour réaliser la fonction OU Voici un circuit électrique simple qui pourrait réaliser la

Searches related to porte logique PDF

Searches related to porte logique PDF

• puis sélectionner l’icône des portes logiques : • dans le menu Affichage cocher « symboles logiques CEI » afin d’avoir les symboles européens • Réaliser alors le montage schématisé ci-contre permettant d'obtenir la table de vérité d'une porte NON

Comment fonctionne une porte logique ?

Une porte logique prend en entré un ou plusieurs bits et génère en sortie un bit de résultat. Ce résultat dépend de l’état des bits en entrée et du type de la porte logique. On représente alors l’ensembles des valeurs d’entrée possibles et leur résultats en sortie dans un tableau nommé la table de vérité.

Quels sont les différents types de portes logiques ?

La porte YES ou OUI en français est la plus basique des portes logiques. Elle prend un seul bit en entrée. Sa fonction copie simplement l’état du bit d’entrée sur le bit de sortie. Donc si le bit d’entrée a pour valeur ‘1’ alors la sortie aura également comme valeur ‘1’ La porte NOT donne en sortie, l’inverse de la valeur du bit d’entrée.

Comment étudier les portes logiques ?

Afin de présenter quelques portes logiques ( elles sont présentes par milliers dans les ordinateurs et permettent d’obtenir une rapidité de calcul impressionnante ) nous allons dans un premier temps, les étudier à l'aide d'un logiciel de simulation déjà utilisé : Crocodile Physics • Ouvrir le lien hypertexte ci-dessus pour accéder au logiciel.

Quels sont les portes logiques et algèbre de Boole ?

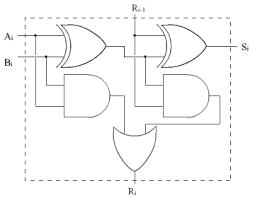

Portes logiques et algèbre de Boole, Système logique. ?C'est un système qui traite l'information de façon logique ?Pour étudier un système logique, il faut connaître les fonctions de base (les composants) et le langage mathématique qui permet de décrire un comportement sous forme d’équations ?Pour un additionneur:

Cours de Systèmes Logiques 1

Portes logiques

Etienne Messerli & Yann Thoma

Reconfigurable and Embedded Digital Systems InstituteHaute Ecole d"Ingénierie et de Gestion du Canton de VaudThis work is licensed under a Creative Commons Attribution-NonCommercial-ShareAlike 3.0 Unported License

Septembre 2019

E. Messerli, Y. Thoma (HES-SO / HEIG-VD / REDS)Portes logiquesSeptembre 2019 1 / 58Plan1Modèles logiques

2Fonctions d"une variable

3Fonctions de plusieurs variables

4Opérateurs complets

5Porte xor

E. Messerli, Y. Thoma (HES-SO / HEIG-VD / REDS)Portes logiquesSeptembre 2019 2 / 58 PlanPolycopié: Electronique numérique

Portes logiques et algèbre de Boole

chapitre 4, pages 35 à 54Circuits logiques combinatoires

Simplification, tables de Karnaugh

chapitres 5-1 à 5-6, pages 55 à 64Symboles utilisés

chapitre 4-9, pages 46 et 47E. Messerli, Y. Thoma (HES-SO / HEIG-VD / REDS)Portes logiquesSeptembre 2019 3 / 58Modèles logiques

Expérience

Soientx1,x2etx3des signaux électroniquesa== 1= =abab 1= =E. Messerli, Y. Thoma (HES-SO / HEIG-VD / REDS)Portes logiquesSeptembre 2019 4 / 58Modèles logiques

Hypothèse 1: Quantification

X3(t) =0si x3(t)v0

X3(t) =1si x3(t)v1

X3(t) =2si v0 E. Messerli, Y. Thoma (HES-SO / HEIG-VD / REDS)Portes logiquesSeptembre 2019 5 / 58Modèles logiques

Hypothèse 2: Délais

Hypothèses: Durée de l"état "2" faible

Plus que 2 états ("0" et "1")

Apparition d"undélai, ouretard, de durée différente...ab ==a E. Messerli, Y. Thoma (HES-SO / HEIG-VD / REDS)Portes logiquesSeptembre 2019 6 / 58 Modèles logiques

Hypothèse 3: Délais constants

Hypothèse : les délais sont tous de durées identiques. Cette durée est constante et indépendante du temps (ne fluctue pas).ab==a a =E. Messerli, Y. Thoma (HES-SO / HEIG-VD / REDS)Portes logiquesSeptembre 2019 7 / 58Modèles logiques

Modèle logique asynchrone

En combinant les hypothèses

de quantification, d"élimination des transitoires, et d"égalisation des délais, nous obtenons le modèle logique asynchrone.E. Messerli, Y. Thoma (HES-SO / HEIG-VD / REDS)Portes logiquesSeptembre 2019 8 / 58

Modèles logiques

Modèle logique combinatoire

En rajoutant que les délais sont nuls, nous obtenons le modèle logique combinatoire. abab== 1=ab =E. Messerli, Y. Thoma (HES-SO / HEIG-VD / REDS)Portes logiquesSeptembre 2019 9 / 58Modèles logiques

Etats Etats d"entrée

Chacune des22=4combinaisons possibles des valeurs des deux entréesx1etx2est appelé état d"entrée.Chacun de ces états sera symbolisé par(x1;x2).De façon générale, chacune des2ncombinaisons des valeurs denentréesx1;x2;;xn

est un état d"entrée(x1;x2;;xn).Etats de sortie Par analogie, chacune des2rcombinaisons des valeurs dersorties est un état de sortie (Z1;Z2;Z3;;Zr)E. Messerli, Y. Thoma (HES-SO / HEIG-VD / REDS)Portes logiquesSeptembre 2019 10 / 58 Modèles logiques

Elément combinatoire

Elément combinatoire : système idéal dont l"état de sortieZest entièrement déterminé par son état d"entrée(x1;x2), en tout temps.a a bE. Messerli, Y. Thoma (HES-SO / HEIG-VD / REDS)Portes logiquesSeptembre 2019 11 / 58Modèles logiques

Fonction logique

La fonction logique d"un élément combinatoire est l"opération réalisée par celui-ci. Elle peut être définie par des équations ou des tables de vérité.Ici, la table de vérité utilisée pour les précédents chronogrammes:

x 1x2Z 0 01 0 11 1 01 1 10 E. Messerli, Y. Thoma (HES-SO / HEIG-VD / REDS)Portes logiquesSeptembre 2019 12 / 58 Modèles logiques

Elément de délai

Par définition, il existe un élément idéal caractérisé par un délai ou retard constant :

.ab E. Messerli, Y. Thoma (HES-SO / HEIG-VD / REDS)Portes logiquesSeptembre 2019 13 / 58Modèles logiques

Systèmes logiques asynchrones

L"usage d"éléments de délai est traité dans le cadre des systèmes logiques asynchrones.aba a 1 1 E. Messerli, Y. Thoma (HES-SO / HEIG-VD / REDS)Portes logiquesSeptembre 2019 14 / 58 Fonctions de plusieurs variables

Théorèmes de commutativité

ab=ba a+b=b+aE. Messerli, Y. Thoma (HES-SO / HEIG-VD / REDS)Portes logiquesSeptembre 2019 37 / 58Fonctions de plusieurs variables

Théorèmes d"idempotence

aa=a a+a=aE. Messerli, Y. Thoma (HES-SO / HEIG-VD / REDS)Portes logiquesSeptembre 2019 38 / 58 Fonctions de plusieurs variables

Théorèmes d"idempotence (2)

Forme généralisée

aaa a=a a+a+a++a=aE. Messerli, Y. Thoma (HES-SO / HEIG-VD / REDS)Portes logiquesSeptembre 2019 39 / 58Fonctions de plusieurs variables

Théorème des constantes

a0=0 a1=a a+0=a a+1=1Démonstration tabulaire : on imposeb=0oub=1dans la table deZ1etZ7E. Messerli, Y. Thoma (HES-SO / HEIG-VD / REDS)Portes logiquesSeptembre 2019 40 / 58

Fonctions de plusieurs variables

Théorèmes de complémentation

aa=0 a+a=1E. Messerli, Y. Thoma (HES-SO / HEIG-VD / REDS)Portes logiquesSeptembre 2019 41 / 58Fonctions de plusieurs variables

Précédence des opérateurs

Le ET a la précédence sur le OU

ab+bd= (ab) + (bd)6=a(b+b)dE. Messerli, Y. Thoma (HES-SO / HEIG-VD / REDS)Portes logiquesSeptembre 2019 42 / 58

Fonctions de plusieurs variables

Théorème de distributivité

On affirme que la fonction ET est distributive par rapport à la fonction OU. a(b+c) =ab+acDe même, la fonction OU est distributive par rapport à la fonction ET. a+bc= (a+b)(a+c)Démonstration tabulaire E. Messerli, Y. Thoma (HES-SO / HEIG-VD / REDS)Portes logiquesSeptembre 2019 43 / 58Fonctions de plusieurs variables

Exercice

Démontrer la relation suivante:

a+ab=a+bE. Messerli, Y. Thoma (HES-SO / HEIG-VD / REDS)Portes logiquesSeptembre 2019 44 / 58 Fonctions de plusieurs variables

Théorèmes d"associativité

a(bc) = (ab)c=abc a+ (b+c) = (a+b) +c=a+b+cDémonstration tabulaire E. Messerli, Y. Thoma (HES-SO / HEIG-VD / REDS)Portes logiquesSeptembre 2019 45 / 58Fonctions de plusieurs variables

Théorèmes du consensus

ax+bx+ab=ax+bx (a+x)(b+x)(a+b) = (a+x)(b+x)Démonstration en séance d"exercices E. Messerli, Y. Thoma (HES-SO / HEIG-VD / REDS)Portes logiquesSeptembre 2019 46 / 58 Opérateurs complets

Fonction NON ET

Z 14=a"b=ab=a+b

La fonctionZ14est appeléefonction NON ET, NAND en anglais, carZ14vaut0siaET bvalentsimultanément1.E. Messerli, Y. Thoma (HES-SO / HEIG-VD / REDS)Portes logiquesSeptembre 2019 47 / 58Opérateurs complets

Fonction NON ET (2)

Z 14=a"b=ab=a+ba

b ab a b ab a b ab= a b ab1a banandb0 01 0 11 1 01 1 10 E. Messerli, Y. Thoma (HES-SO / HEIG-VD / REDS)Portes logiquesSeptembre 2019 48 / 58 Opérateurs complets

Opérateur complet

On appelle OPERATEUR COMPLET tout opérateur (porte) dont trois assemblages distincts permettent de réaliser les trois fonctions NON, ET et OU.Ainsi, suivant cette definition, la porte NAND est un OPERATEUR COMPLET.

E. Messerli, Y. Thoma (HES-SO / HEIG-VD / REDS)Portes logiquesSeptembre 2019 49 / 58Opérateurs complets

Fonction NON OU

Z 8=a#b=a+b=ab

La fonctionZ8est appeléefonction NON OU, NOR en anglais, carZ8vaut0siaETb valentsimultanément0.E. Messerli, Y. Thoma (HES-SO / HEIG-VD / REDS)Portes logiquesSeptembre 2019 50 / 58

Opérateurs complets

Fonction NON OU (2)

Z 8=a#b=a+b=aba

b ab a b ab a b ab=1 a b aba banorb0 01 0 10 1 00 1 10 E. Messerli, Y. Thoma (HES-SO / HEIG-VD / REDS)Portes logiquesSeptembre 2019 51 / 58Opérateurs complets

Théorèmes de De Morgan

Théorèmes de De Morgan

ab=a+b a+b=ab Démonstration tabulaire

E. Messerli, Y. Thoma (HES-SO / HEIG-VD / REDS)Portes logiquesSeptembre 2019 52 / 58 Opérateurs complets

Théorèmes de De Morgan (Corollaires)

Théorèmes de De Morgan (Corollaires)

ab=a+b a+b=ab Démonstration algébrique

E. Messerli, Y. Thoma (HES-SO / HEIG-VD / REDS)Portes logiquesSeptembre 2019 53 / 58Opérateurs complets

Définition

Un produit de plusieurs variables apparaissant chacune sous la forme vraie ou inversée est unmonôme.Une somme de produits (ou monômes) est un polynôme. Exemples de monômes:ab,abcExemple de polynôme:ab+abcE. Messerli, Y. Thoma (HES-SO / HEIG-VD / REDS)Portes logiquesSeptembre 2019 54 / 58

Opérateurs complets

Exemple

Grâce à De Morgan, écrivez la fonction suivante sous la forme d"un polynôme: Z=a+b+cdE. Messerli, Y. Thoma (HES-SO / HEIG-VD / REDS)Portes logiquesSeptembre 2019 55 / 58Opérateurs complets

Transformation de logigrammesa

b ab a b ab a b ab a b abE. Messerli, Y. Thoma (HES-SO / HEIG-VD / REDS)Portes logiquesSeptembre 2019 56 / 58 Porte xor

Fonction OU-exclusif

Z 6=ab=ab+ab

La fonctionZ6est appeléefonction OU-exclusif, XOR en anglais, carZ14vaut0si soit asoitbvaut1.a b ab=1 a baba baxorbaxorb0 001 0 110 1 010 1 101 E. Messerli, Y. Thoma (HES-SO / HEIG-VD / REDS)Portes logiquesSeptembre 2019 57 / 58Porte xor Fonction OU-exclusif: théorèmes

ab=ba aa=0 a0=a a1=a aa=1ab=ab+ab=ab=abE. Messerli, Y. Thoma (HES-SO / HEIG-VD / REDS)Portes logiquesSeptembre 2019 58 / 58

quotesdbs_dbs17.pdfusesText_23

E. Messerli, Y. Thoma (HES-SO / HEIG-VD / REDS)Portes logiquesSeptembre 2019 5 / 58Modèles logiques

Hypothèse 2: Délais

Hypothèses: Durée de l"état "2" faible

Plus que 2 états ("0" et "1")

Apparition d"undélai, ouretard, de durée différente...ab ==a E. Messerli, Y. Thoma (HES-SO / HEIG-VD / REDS)Portes logiquesSeptembre 2019 6 / 58Modèles logiques

Hypothèse 3: Délais constants

Hypothèse : les délais sont tous de durées identiques. Cette durée est constante et indépendante du temps (ne fluctue pas).ab==a a=E. Messerli, Y. Thoma (HES-SO / HEIG-VD / REDS)Portes logiquesSeptembre 2019 7 / 58Modèles logiques

Modèle logique asynchrone

En combinant les hypothèses

de quantification, d"élimination des transitoires, et d"égalisation des délais, nous obtenons lemodèle logique asynchrone.E. Messerli, Y. Thoma (HES-SO / HEIG-VD / REDS)Portes logiquesSeptembre 2019 8 / 58

Modèles logiques

Modèle logique combinatoire

En rajoutant que les délais sont nuls, nous obtenons le modèle logique combinatoire. abab== 1=ab=E. Messerli, Y. Thoma (HES-SO / HEIG-VD / REDS)Portes logiquesSeptembre 2019 9 / 58Modèles logiques

EtatsEtats d"entrée

Chacune des22=4combinaisons possibles des valeurs des deux entréesx1etx2estappelé état d"entrée.Chacun de ces états sera symbolisé par(x1;x2).De façon générale, chacune des2ncombinaisons des valeurs denentréesx1;x2;;xn

est un état d"entrée(x1;x2;;xn).Etats de sortie Par analogie, chacune des2rcombinaisons des valeurs dersorties est un état de sortie (Z1;Z2;Z3;;Zr)E. Messerli, Y. Thoma (HES-SO / HEIG-VD / REDS)Portes logiquesSeptembre 2019 10 / 58Modèles logiques

Elément combinatoire

Elément combinatoire : système idéal dont l"état de sortieZest entièrement déterminé par son état d"entrée(x1;x2), en tout temps.a abE. Messerli, Y. Thoma (HES-SO / HEIG-VD / REDS)Portes logiquesSeptembre 2019 11 / 58Modèles logiques

Fonction logique

La fonction logique d"un élément combinatoire est l"opération réalisée par celui-ci.Elle peut être définie par des équations ou des tables de vérité.Ici, la table de vérité utilisée pour les précédents chronogrammes:

x 1x2Z 0 01 0 11 1 01 1 10 E. Messerli, Y. Thoma (HES-SO / HEIG-VD / REDS)Portes logiquesSeptembre 2019 12 / 58Modèles logiques

Elément de délai

Par définition, il existe un élément idéal caractérisé par un délai ou retard constant :

.abE. Messerli, Y. Thoma (HES-SO / HEIG-VD / REDS)Portes logiquesSeptembre 2019 13 / 58Modèles logiques

Systèmes logiques asynchrones

L"usage d"éléments de délai est traité dans le cadre des systèmes logiques asynchrones.aba a 1 1 E. Messerli, Y. Thoma (HES-SO / HEIG-VD / REDS)Portes logiquesSeptembre 2019 14 / 58Fonctions de plusieurs variables

Théorèmes de commutativité

ab=baa+b=b+aE. Messerli, Y. Thoma (HES-SO / HEIG-VD / REDS)Portes logiquesSeptembre 2019 37 / 58Fonctions de plusieurs variables

Théorèmes d"idempotence

aa=a a+a=aE. Messerli, Y. Thoma (HES-SO / HEIG-VD / REDS)Portes logiquesSeptembre 2019 38 / 58Fonctions de plusieurs variables

Théorèmes d"idempotence (2)

Forme généralisée

aaa a=aa+a+a++a=aE. Messerli, Y. Thoma (HES-SO / HEIG-VD / REDS)Portes logiquesSeptembre 2019 39 / 58Fonctions de plusieurs variables

Théorème des constantes

a0=0 a1=a a+0=aa+1=1Démonstration tabulaire : on imposeb=0oub=1dans la table deZ1etZ7E. Messerli, Y. Thoma (HES-SO / HEIG-VD / REDS)Portes logiquesSeptembre 2019 40 / 58

Fonctions de plusieurs variables

Théorèmes de complémentation

aa=0a+a=1E. Messerli, Y. Thoma (HES-SO / HEIG-VD / REDS)Portes logiquesSeptembre 2019 41 / 58Fonctions de plusieurs variables

Précédence des opérateurs

Le ET a la précédence sur le OU

ab+bd= (ab) + (bd)6=a(b+b)dE. Messerli, Y. Thoma (HES-SO / HEIG-VD / REDS)Portes logiquesSeptembre 2019 42 / 58

Fonctions de plusieurs variables

Théorème de distributivité

On affirme que la fonction ET est distributive par rapport à la fonction OU. a(b+c) =ab+acDe même, la fonction OU est distributive par rapport à la fonction ET. a+bc= (a+b)(a+c)Démonstration tabulaireE. Messerli, Y. Thoma (HES-SO / HEIG-VD / REDS)Portes logiquesSeptembre 2019 43 / 58Fonctions de plusieurs variables

Exercice

Démontrer la relation suivante:

a+ab=a+bE. Messerli, Y. Thoma (HES-SO / HEIG-VD / REDS)Portes logiquesSeptembre 2019 44 / 58Fonctions de plusieurs variables

Théorèmes d"associativité

a(bc) = (ab)c=abc a+ (b+c) = (a+b) +c=a+b+cDémonstration tabulaireE. Messerli, Y. Thoma (HES-SO / HEIG-VD / REDS)Portes logiquesSeptembre 2019 45 / 58Fonctions de plusieurs variables

Théorèmes du consensus

ax+bx+ab=ax+bx (a+x)(b+x)(a+b) = (a+x)(b+x)Démonstration en séance d"exercices E. Messerli, Y. Thoma (HES-SO / HEIG-VD / REDS)Portes logiquesSeptembre 2019 46 / 58Opérateurs complets

Fonction NON ET

Z14=a"b=ab=a+b

La fonctionZ14est appeléefonction NON ET, NAND en anglais, carZ14vaut0siaETbvalentsimultanément1.E. Messerli, Y. Thoma (HES-SO / HEIG-VD / REDS)Portes logiquesSeptembre 2019 47 / 58Opérateurs complets

Fonction NON ET (2)

Z14=a"b=ab=a+ba

b ab a b ab a b ab= a b ab1a banandb0 01 0 11 1 01 1 10 E. Messerli, Y. Thoma (HES-SO / HEIG-VD / REDS)Portes logiquesSeptembre 2019 48 / 58Opérateurs complets

Opérateur complet

On appelle OPERATEUR COMPLET tout opérateur (porte) dont trois assemblagesdistincts permettent de réaliser les trois fonctions NON, ET et OU.Ainsi, suivant cette definition, la porte NAND est un OPERATEUR COMPLET.

E. Messerli, Y. Thoma (HES-SO / HEIG-VD / REDS)Portes logiquesSeptembre 2019 49 / 58Opérateurs complets

Fonction NON OU

Z8=a#b=a+b=ab

La fonctionZ8est appeléefonction NON OU, NOR en anglais, carZ8vaut0siaETbvalentsimultanément0.E. Messerli, Y. Thoma (HES-SO / HEIG-VD / REDS)Portes logiquesSeptembre 2019 50 / 58

Opérateurs complets

Fonction NON OU (2)

Z8=a#b=a+b=aba

b ab a b ab a b ab=1 a b aba banorb0 01 0 10 1 00 1 10E. Messerli, Y. Thoma (HES-SO / HEIG-VD / REDS)Portes logiquesSeptembre 2019 51 / 58Opérateurs complets

Théorèmes de De Morgan

Théorèmes de De Morgan

ab=a+b a+b=abDémonstration tabulaire

E. Messerli, Y. Thoma (HES-SO / HEIG-VD / REDS)Portes logiquesSeptembre 2019 52 / 58Opérateurs complets

Théorèmes de De Morgan (Corollaires)

Théorèmes de De Morgan (Corollaires)

ab=a+b a+b=abDémonstration algébrique

E. Messerli, Y. Thoma (HES-SO / HEIG-VD / REDS)Portes logiquesSeptembre 2019 53 / 58Opérateurs complets

Définition

Un produit de plusieurs variables apparaissant chacune sous la forme vraie ou inversée est unmonôme.Une somme de produits (ou monômes) est un polynôme.Exemples de monômes:ab,abcExemple de polynôme:ab+abcE. Messerli, Y. Thoma (HES-SO / HEIG-VD / REDS)Portes logiquesSeptembre 2019 54 / 58

Opérateurs complets

Exemple

Grâce à De Morgan, écrivez la fonction suivante sous la forme d"un polynôme:Z=a+b+cdE. Messerli, Y. Thoma (HES-SO / HEIG-VD / REDS)Portes logiquesSeptembre 2019 55 / 58Opérateurs complets

Transformation de logigrammesa

b ab a b ab a b ab a b abE. Messerli, Y. Thoma (HES-SO / HEIG-VD / REDS)Portes logiquesSeptembre 2019 56 / 58Porte xor

Fonction OU-exclusif

Z6=ab=ab+ab

La fonctionZ6est appeléefonction OU-exclusif, XOR en anglais, carZ14vaut0si soit asoitbvaut1.a b ab=1 a baba baxorbaxorb0 001 0 110 1 010 1 101 E. Messerli, Y. Thoma (HES-SO / HEIG-VD / REDS)Portes logiquesSeptembre 2019 57 / 58Porte xorFonction OU-exclusif: théorèmes

ab=ba aa=0 a0=a a1=aaa=1ab=ab+ab=ab=abE. Messerli, Y. Thoma (HES-SO / HEIG-VD / REDS)Portes logiquesSeptembre 2019 58 / 58

quotesdbs_dbs17.pdfusesText_23[PDF] Portée sociale

[PDF] Portrait et plan d'action en Montérégie (TransformAction). ? Opportunités de marché significatives pour les aliments régionaux. ? Intérêt pour la form

[PDF] portrait plus précis de l'état actuel du secteur touristique canadien. Toutefois

[PDF] poser des question et avoir la reponse

[PDF] poser des questions et l'inversion du sujet

[PDF] poser des questions et prendre des notes

[PDF] poser des questions formelles et informelles

[PDF] Positionnement initial de la négation dans la phrase en latin

[PDF] possibles

[PDF] poster pour présenter ses goûts et en POC / PPC = présentation orale de posters ) ... verbes de goût + V ing ... TE : dialogue + 1 phrase sur ses goût

[PDF] potentialités et contraintes du territoire français 1ere s

[PDF] potentialités et contraintes du territoire français carte

[PDF] potentialités et contraintes du territoire français composition

[PDF] potentialités et contraintes du territoire français controle