Corrigé de lexamen final_TS412

Corrigé de lexamen final_TS412

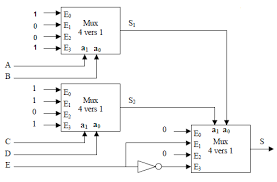

Exercice 01 (04 5 pts). A. Réaliser les fonctions booléennes suivantes à l'aide le multiplexeur ne suffit pas à lui seul pour générer la fonction F4. Une ...

Université des Sciences et de la Technologie dOran Faculté des

Université des Sciences et de la Technologie dOran Faculté des

Donner la fonction algébrique d'un multiplexeur 8 vers 1. Corrigé. Un multiplexeur informatiques : Cours et exercices corrigés 3° édition

TD systèmes logiques.pdf

TD systèmes logiques.pdf

Exercice 7: 1) Créer un circuit pour mettre en œuvre la fonction logique spécifiée au tableau suivant en utilisant un multiplexeur à 8 entrées.

Exercice 1: Utilisation dun multiplexeur

Exercice 1: Utilisation dun multiplexeur

Exercice 1: Utilisation d'un multiplexeur. Implanter la fonction suivante à l'aide d'un multiplexeur puis en calculer le coût. = ∏(03

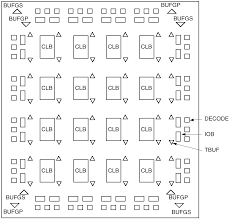

ELA114 : conception numérique en VHDL

ELA114 : conception numérique en VHDL

2.2.4 Le multiplexeur. Le multiplexeur est la fonction inverse du démultiplexeur. C'est un sélecteur de données ou aiguillage convergent. Il peut transformer

ELECTRONIQUE NUMERIQUE Logique combinatoire et multiplexage

ELECTRONIQUE NUMERIQUE Logique combinatoire et multiplexage

en mode de fonctionnement normal plusieurs entrées peuvent être activées simultanément. 15- Exercice 15 : (Multiplexeur). Établisser la table de vérité du

Exercices corrigés (architecture ordinateurs et circuits logiques)

Exercices corrigés (architecture ordinateurs et circuits logiques)

3) Multiplexeurs (MUX pour les intimes). 3-a) On a ce schéma de multiplexeur 1 parmi 4. Qu'obtient-on en sortie cette sortie S étant seulement fonction des

Multiplexeur 74151

Multiplexeur 74151

Exercice 2. 1. ̅. ̅. ̅. 2. ̅. ̅. ̅.

Untitled

Untitled

Réaliser en utilisant un Multiplexeur de deux entrées d'adresse : A et B. Exercice IV : ( 6 pts). 1. Compléter le montage ci-après pour réaliser un compteur ...

Exercices de Révision sur les Circuits Combinatoires Multiplexeur

Exercices de Révision sur les Circuits Combinatoires Multiplexeur

Combinatoires Multiplexeur

Corrigé de lexamen final_TS412

Corrigé de lexamen final_TS412

Corrigé de l'examen final Exercice 01 (04 5 pts) ... B. En utilisant un multiplexeur 8 vers 1 et des portes logiques

TD systèmes logiques.pdf

TD systèmes logiques.pdf

Exercice 7: 1) Créer un circuit pour mettre en œuvre la fonction logique spécifiée au tableau suivant en utilisant un multiplexeur à 8 entrées.

Logique combinatoire et multiplexage

Logique combinatoire et multiplexage

1- Exercice 1 : (Centrale). La fonction Multiplexeur 2 vers 1 dont le symbole logique est représenté Figure 1

Multiplexeurs et Dmultiplexeurs

Multiplexeurs et Dmultiplexeurs

Un multiplexeur ou sélecteur de données est un commutateur qui va pouvoir à l'aide de n bits d'adresse

GELE2442 - Chapitre 5

GELE2442 - Chapitre 5

On verra des circuits communs qui permettent de réaliser des fonctions plus générales : décodeurs encodeurs

Introduction aux circuits logiques de base

Introduction aux circuits logiques de base

– Un circuit de décalage. – Additionneur. – Unité arithmétique et logique. Page 61. 61. IFT1215. Introduction aux systèmes informatiques. Multiplexeur. • Le

TP N° 5 : Simulations de composants passifs: coupleurs

TP N° 5 : Simulations de composants passifs: coupleurs

Exercice 2 : Multiplexeurs/demultiplexeurs : a) Réaliser le schéma suivant : b) Vérifier que sans pertes en exces le multiplexeur mélange bien les deux

Université Aboubakr Belkaid Faculté des Sciences Département des

Université Aboubakr Belkaid Faculté des Sciences Département des

Exercice 1 : Analyser les circuits logiques suivants : Synthétiser cette fonction avec un multiplexeur 8 1. ... Corrigé série 1. Exercice 1.

Présentation PowerPoint

Présentation PowerPoint

Le taux d'activité. • Le type d'application possible. Pr D. El Ghanami. Page 30. 30. Exercice 2: Un multiplexeur temporel supporte N voies basse vitesse à 64

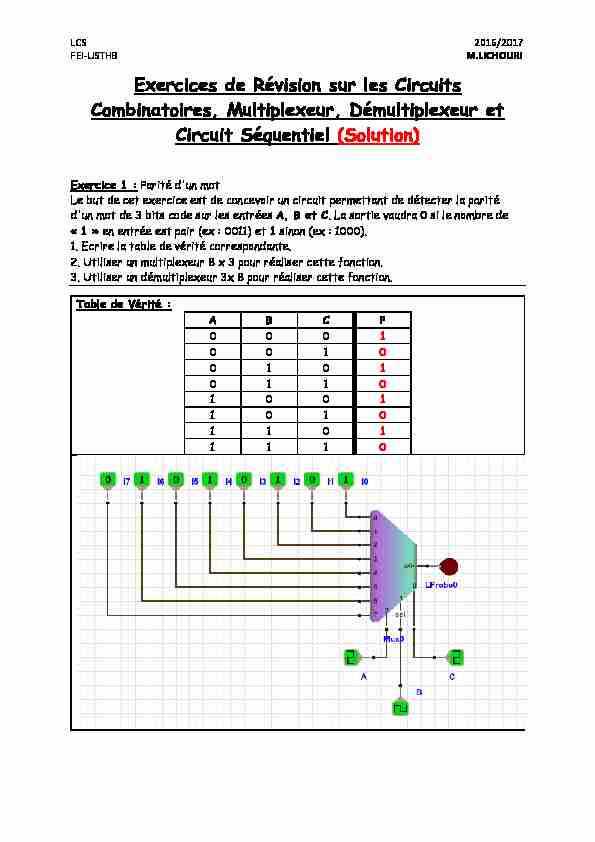

LCS 2016/2017

FEI-USTHB M.LICHOURI

Exercices de Révision sur les Circuits

Combinatoires, Multiplexeur, Démultiplexeur et

Circuit Séquentiel (Solution)

Exercice 1 : Parité d'un mot

Le but de cet exercice est de concevoir un circuit permettant de détecter la parité d'un mot de 3 bits code sur les entrées A, B et C. La sortie vaudra 0 si le nombre de " 1 » en entrée est pair (ex : 0011) et 1 sinon (ex : 1000).1. Ecrire la table de vérité correspondante.

2. Utiliser un multiplexeur 8 x 3 pour réaliser cette fonction.

3. Utiliser un démultiplexeur 3x 8 pour réaliser cette fonction.

Table de Vérité :

A B C P

0 0 0 1

0 0 1 0

0 1 0 1

0 1 1 0

1 0 0 1

1 0 1 0

1 1 0 1

1 1 1 0

LCS 2016/2017

FEI-USTHB M.LICHOURI

Exercice 2 : Incrémenteur

Une (grande) partie des additions effectuées par un ordinateur consistent simplement a ajouter 1 a une autre valeur x (on incrémente la valeur x).1. Réaliser un incrémenter 3 bit avec retenue de sortie (Entrées A0A1A2 ; Sorties

RI0I1I2).

2. Réaliser aussi le circuit d'un décrémenteur 3 bits, avec " 000 » cas indéfinis

(Entrées A0A1A2 ; Sorties D0D1D2).3. Réaliser la fonction D0 avec un 0X[ GH 3 HQPUpHV G·MGUHVVHs.

4. Réaliser la fonction D1 avec un G(0X[ GH 3 HQPUpHV G·MGUHVVHs.

5. Réaliser la fonction D2 avec un DEMux de 1x4 et un Mux 4x1.

Table de Vérité :

A0 A1 A2 R I0 I1 I2

0 0 0 0 0 0 1

0 0 1 0 0 1 0

0 1 0 0 0 1 1

0 1 1 0 1 0 0

1 0 0 0 1 0 1

1 0 1 0 1 1 0

1 1 0 0 1 1 1

1 1 1 1 0 0 0

Table de Vérité :

LCS 2016/2017

FEI-USTHB M.LICHOURI

A0 A1 A2 D0 D1 D2

0 0 0 0 0 0

0 0 1 0 0 0

0 1 0 0 0 1

0 1 1 0 1 0

1 0 0 0 1 1

1 0 1 1 0 0

1 1 0 1 0 1

1 1 1 1 1 0

LCS 2016/2017

FEI-USTHB M.LICHOURI

Exercice 3 : Rotation

On aime concevoir un circuit qui fait la rotation de 3 bit (CBA) à droite ou à gaucheVHORQ OM YMOHXU G·XQH YMULMNOH HQ HQPUpH GB

Ex : DCBA=0100 => D=0 (rotation à gauche) ; résultat (R0R1R2=001) DCBA=1100 => D=1 (rotation à droite) ; résultat (R0R1R2=010)1. Donner la table de vérité du circuit.

2. Donner les deux formes canoniques des sorties.

3. Réaliser les trois sorties avec des portes Nand ou Nor seulement.

LCS 2016/2017

FEI-USTHB M.LICHOURI

Exercice 4 :

Réaliser le circuit qui permet d'effectuer le complément à deux G·XQ QRPNUH NLQMLUH de3 bits j O·MLGH GH 3 Mux 8x1.

A B C M0 M1 M2

0 0 0 0 0 0

0 0 1 1 1 1

0 1 0 1 1 0

0 1 1 1 0 1

1 0 0 1 0 0

1 0 1 0 1 1

1 1 0 0 1 0

1 1 1 0 0 1

LCS 2016/2017

FEI-USTHB M.LICHOURI

Exercice 5 : Incrément de 5

Le code ROT5 permet de faire la rotation d'un nombre binaire en ajoutant 5 en binaire, sans retenue.Ex : ROT5(0000)=0101 ; ROT5(1111)=0100

Réaliser le circuit de conversion de binaire au ROT5 en utilisant un décodeur de 4 à 16 et 4 portes Or.LCS 2016/2017

FEI-USTHB M.LICHOURI

A B C D R0 R1 R2 R3

0 0 0 0 0 1 0 1

0 0 0 1 0 1 1 0

0 0 1 0 0 1 1 1

0 0 1 1 1 0 0 0

0 1 0 0 1 0 0 1

0 1 0 1 1 0 1 0

0 1 1 0 1 0 1 1

0 1 1 1 1 1 0 0

1 0 0 0 1 1 0 1

1 0 0 1 1 1 1 0

1 0 1 0 1 1 1 1

1 0 1 1 0 0 0 0

1 1 0 0 0 0 0 1

1 1 0 1 0 0 1 0

1 1 1 0 0 1 0 0

1 1 1 1 0 1 0 1

LCS 2016/2017

FEI-USTHB M.LICHOURI

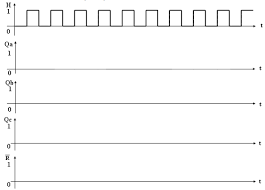

Exercice 6 : Circuit Séquentiel

1. Trouvez la fonction Ft en fonction de A, B, C et D et Ft-1 à partir du circuit suivant.

2. Donnez la table de vérité réduite et éclaté de F pour C=D=1.

Si C=D=1 :

A B F 0 0 1 0 1 0 1 0 1 1 1 1LCS 2016/2017

FEI-USTHB M.LICHOURI

Exercice 7 :

En utilisant la table de transition de la bascule CD ; transformer la bascule CD enBascule RS.

Qn Qn+1 C D

0 0 0 x

0 1 x 1

1 0 0 1

1 1 1 0

Qn R S Qn+1 C D

0 0 0 0 0 x

0 0 1 1 x 1

0 1 0 0 0 x

0 1 1 x x x

1 0 0 1 1 0

1 0 1 1 1 0

1 1 0 0 0 1

1 1 1 x x x

quotesdbs_dbs2.pdfusesText_2[PDF] les nombres complexes cours 2 bac

[PDF] les nombres complexes cours bac

[PDF] les nombres complexes cours bac pc

[PDF] les nombres complexes cours cm2

[PDF] les nombres complexes cours et exercices corrigés pdf

[PDF] les nombres complexes. cours maths sup

[PDF] les nombres premiers 5ème

[PDF] les ondes électromagnétiques

[PDF] les ondes électromagnétiques cours

[PDF] les ondes électromagnétiques danger

[PDF] les ondes électromagnétiques du téléphone portable

[PDF] les ondes électromagnétiques et la santé

[PDF] les ondes électromagnétiques pdf

[PDF] les ondes électromagnétiques sur la santé