Exercices de Révision sur les Circuits Combinatoires Multiplexeur

Exercices de Révision sur les Circuits Combinatoires Multiplexeur

Exercices de Révision sur les Circuits. Combinatoires Multiplexeur

Corrigé de lexamen final_TS412

Corrigé de lexamen final_TS412

Exercice 01 (04 5 pts). A. Réaliser les fonctions booléennes suivantes à l'aide le multiplexeur ne suffit pas à lui seul pour générer la fonction F4. Une ...

Université des Sciences et de la Technologie dOran Faculté des

Université des Sciences et de la Technologie dOran Faculté des

Donner la fonction algébrique d'un multiplexeur 8 vers 1. Corrigé. Un multiplexeur informatiques : Cours et exercices corrigés 3° édition

TD systèmes logiques.pdf

TD systèmes logiques.pdf

Exercice 7: 1) Créer un circuit pour mettre en œuvre la fonction logique spécifiée au tableau suivant en utilisant un multiplexeur à 8 entrées.

Exercice 1: Utilisation dun multiplexeur

Exercice 1: Utilisation dun multiplexeur

Exercice 1: Utilisation d'un multiplexeur. Implanter la fonction suivante à l'aide d'un multiplexeur puis en calculer le coût. = ∏(03

ELA114 : conception numérique en VHDL

ELA114 : conception numérique en VHDL

2.2.4 Le multiplexeur. Le multiplexeur est la fonction inverse du démultiplexeur. C'est un sélecteur de données ou aiguillage convergent. Il peut transformer

ELECTRONIQUE NUMERIQUE Logique combinatoire et multiplexage

ELECTRONIQUE NUMERIQUE Logique combinatoire et multiplexage

en mode de fonctionnement normal plusieurs entrées peuvent être activées simultanément. 15- Exercice 15 : (Multiplexeur). Établisser la table de vérité du

Exercices corrigés (architecture ordinateurs et circuits logiques)

Exercices corrigés (architecture ordinateurs et circuits logiques)

3) Multiplexeurs (MUX pour les intimes). 3-a) On a ce schéma de multiplexeur 1 parmi 4. Qu'obtient-on en sortie cette sortie S étant seulement fonction des

Multiplexeur 74151

Multiplexeur 74151

Exercice 2. 1. ̅. ̅. ̅. 2. ̅. ̅. ̅.

Untitled

Untitled

Réaliser en utilisant un Multiplexeur de deux entrées d'adresse : A et B. Exercice IV : ( 6 pts). 1. Compléter le montage ci-après pour réaliser un compteur ...

Exercices de Révision sur les Circuits Combinatoires Multiplexeur

Exercices de Révision sur les Circuits Combinatoires Multiplexeur

Combinatoires Multiplexeur

Corrigé de lexamen final_TS412

Corrigé de lexamen final_TS412

Corrigé de l'examen final Exercice 01 (04 5 pts) ... B. En utilisant un multiplexeur 8 vers 1 et des portes logiques

TD systèmes logiques.pdf

TD systèmes logiques.pdf

Exercice 7: 1) Créer un circuit pour mettre en œuvre la fonction logique spécifiée au tableau suivant en utilisant un multiplexeur à 8 entrées.

Logique combinatoire et multiplexage

Logique combinatoire et multiplexage

1- Exercice 1 : (Centrale). La fonction Multiplexeur 2 vers 1 dont le symbole logique est représenté Figure 1

Multiplexeurs et Dmultiplexeurs

Multiplexeurs et Dmultiplexeurs

Un multiplexeur ou sélecteur de données est un commutateur qui va pouvoir à l'aide de n bits d'adresse

GELE2442 - Chapitre 5

GELE2442 - Chapitre 5

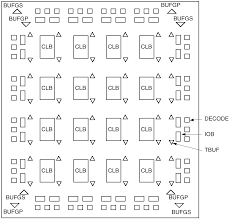

On verra des circuits communs qui permettent de réaliser des fonctions plus générales : décodeurs encodeurs

Introduction aux circuits logiques de base

Introduction aux circuits logiques de base

– Un circuit de décalage. – Additionneur. – Unité arithmétique et logique. Page 61. 61. IFT1215. Introduction aux systèmes informatiques. Multiplexeur. • Le

TP N° 5 : Simulations de composants passifs: coupleurs

TP N° 5 : Simulations de composants passifs: coupleurs

Exercice 2 : Multiplexeurs/demultiplexeurs : a) Réaliser le schéma suivant : b) Vérifier que sans pertes en exces le multiplexeur mélange bien les deux

Université Aboubakr Belkaid Faculté des Sciences Département des

Université Aboubakr Belkaid Faculté des Sciences Département des

Exercice 1 : Analyser les circuits logiques suivants : Synthétiser cette fonction avec un multiplexeur 8 1. ... Corrigé série 1. Exercice 1.

Présentation PowerPoint

Présentation PowerPoint

Le taux d'activité. • Le type d'application possible. Pr D. El Ghanami. Page 30. 30. Exercice 2: Un multiplexeur temporel supporte N voies basse vitesse à 64

Université Aboubakr Belkaid Faculté des Sciences Département des Mathématiques

Planche d"Exercices N

01Circuits Combinatoires

L1 - MI - S2 / 2019-2020

Le savoir qui compte est celui qu"on se donne soi-même par curiosité, passion de savoir.P. Léautaud

Exercice 1

: Analyser les circuits logiques suivants :Exercice 2

: Concevoir un circuit qui permet de faire l"addition ou la soustraction (additionneur/soustracteur) de deux nombres binaires A et B de 1 bit. On rappelle que dans la représentation en complément à 2,1++=-BABA. Cet additionneur/soustracteur possèdera une entrée de

commande C qui sera utilisée comme suit :· C=0, fonctionnement en addition.

· C=1, fonctionnement en soustraction.

En utilisant ce schéma bloc de additionneur-soustracteur, dessiner un schéma bloc d"un additionneur -

soustracteur en parallèle à 4 bits, c"est-à-dire un circuit logique qui peut faire la somme des nombres

binaires0123AAAAA= et 0123BBBBB= si C=0 et A-B si C=1.

Exercice 3

1. Soit la fonction combinatoire f(x,y,z) définie par la table de Karnaugh ci dessous

1. Synthétiser cette fonction avec un multiplexeur 8 չ 1.

2. Synthétiser cette fonction avec un multiplexeur 4 չ 1.

Exercice 4

Faire la synthèse d"un multiplexeur 2 vers 1.

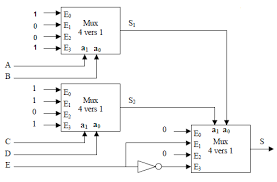

En utilisant le schéma bloc ci-dessous,

réalisé le schéma bloc d"un multiplexeur 4 vers 1 en utilisant que trois multiplexeurs 2 vers 1. c ab 0 100 0 1 11 10

1 0 1 1

1 1 1 0

Mux2 vers 1 0

1 y D0 D1 S 0Mux 2→1

Exercice 5

On veut réaliser un transcodeur permettant de convertir un nombre en binaireABC vers le binaire naturel XYZ

et Z.1. Dresser une table de v

érité traduisant le fonctionnement,

2. A l"aide du tableau de Karnaugh, trouve

3. Donner le logigramme de ce transcodeur.

4. Dessiner le logigramme avec uniquement des portes "XOR" à deux entrées,

5. En déduire le logigramme si

Annexe

A B C On veut réaliser un transcodeur permettant de convertir un nombre en binaire XYZ. Ce transcodeur a trois entrées : A, B et Cérité traduisant le fonctionnement,

A l"aide du tableau de Karnaugh, trouver les équations des sorties : XDonner le logigramme de ce transcodeur.

Dessiner le logigramme avec uniquement des portes "XOR" à deux entrées, En déduire le logigramme si le code d"entrée est sur 4 bits.Transcodeur

du binaire réfléchi vers binaire naturel. X Y ZOn veut réaliser un transcodeur permettant de convertir un nombre en binaire réfléchi de trois bits

: A, B et C et trois sorties X, Y r les équations des sorties : X, Y et Z, Dessiner le logigramme avec uniquement des portes "XOR" à deux entrées,Corrigé série 1

Exercice 1

1. Expression logique :

( )()().....,,,11001100001010yxyxyxyxyxyyxxfÅÅ=Å+= Table de vérité0x 1x 0y 1y 00yxÅ ()11yxÅ ()1010,,,yyxxf

0 0 0 0 0 0 0 0 1 1 1 1 1 1 11 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 1 1 0 0 1 1 0 0 0 0 1 1 0 0 1 1 1 0 1 0 0 1 0 1 1 0 1 0 0 1 0 1 1 0 0 0 0 1 0 0 0 0 1 0 0 0 0 1

Puisque ()101010101,,,yyxxsiyyxxf==donc ce circuit est un comparateur d"égalité de nombres binaires à deux bits.2. Expression logique : .,,,44433322211BSBBSBBSBBS=Å=Å=Å= Table de vérité

4B 3B 2B 1B 4S 3S 2S 1S

0 0 0 0 0 0 0 0 1 1 1 1 1 1 11 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0

Ce circuit réalise la conversion en code de Gray d"un nombre binaire de quatre bits.Exercice 2

B C S

0 0 0

0 1 1

1 0 1

1 1 0

...BCBCBCSÅ=+=Exercice 3

1. Réalisation de la fonction f avec un MUX 8չ1.

2. Réalisation de la fonction f avec un

MUX4չ1.

Exercice 4

Synthèse d"un MUX à 2 entrées

Symbole logique d"un MUX 2 չ 1

Ce MUX possède une lignes de sélection des données, puisqu"il est possible de sélectionner

l"une ou l"autre des 2 lignes d"entrée de données avec seulement un bit. Soit, la table de vérité

suivante : MUX 0 01 Entrées de données

???310DDEntrée de Sélection S0

y sortie des données G0/1 MUX 0 1 0 1 2 3 b a cY sortie des

données 1 MUX c b a 0 1 2 3 4 5 6 7 1 210G70 y C B A Csor S A B

Csor Cen

S A B

C sor CenS A B

C sor CenS A B

C sor Cen SA0 B0 A1 B1 A2 B2 A3 B3

0S 1S 2S 3S

0C 1C 2C 3C C

Entrée de sélection

0SEntrée sélectionnée

0 0D 1 1DLa sortie des données est égale à

0Dseulement si 00=S : 00SDY=.

La sortie des données est égale à 1Dseulement si 10=S : 01SDY=.D"où la fonction de sortie :

..0100SDSDY+=.Soit, le logigramme correspondant est :

MUX 2չ1

Exercice 5

Table de vérité

a b c x y z0 0 0 0 0 0

0 0 1 0 0 1

0 1 0 0 1 1

0 1 1 0 1 0

1 0 0 1 1 1

1 0 1 1 1 0

1 1 0 1 0 0

1 1 1 1 0 1

Expressions logiques

cbazbayax Mux2 vers 1 0

1 y 1 D2 D3 S0 0 Mux2 vers 1 0

1 y 0 D0 D1 0 Mux2 vers 1 0

1 y S1 0quotesdbs_dbs10.pdfusesText_16[PDF] les nombres complexes cours 2 bac

[PDF] les nombres complexes cours bac

[PDF] les nombres complexes cours bac pc

[PDF] les nombres complexes cours cm2

[PDF] les nombres complexes cours et exercices corrigés pdf

[PDF] les nombres complexes. cours maths sup

[PDF] les nombres premiers 5ème

[PDF] les ondes électromagnétiques

[PDF] les ondes électromagnétiques cours

[PDF] les ondes électromagnétiques danger

[PDF] les ondes électromagnétiques du téléphone portable

[PDF] les ondes électromagnétiques et la santé

[PDF] les ondes électromagnétiques pdf

[PDF] les ondes électromagnétiques sur la santé