Examen final – INF2500 Architecture des ordinateurs Automne

Examen final – INF2500 Architecture des ordinateurs Automne

horloge du processeur sur le RAS et 6 périodes horloge du processeur sur le CAS. L'ordinateur sera utilisé principalement dans des applications où l'accès à

ARCHITECTURE DES ORDINATEURS Corrigé Examen Décembre

ARCHITECTURE DES ORDINATEURS Corrigé Examen Décembre

MICROARCHITECTURES ET TEMPS D'EXECUTION DE PROGRAMMES. La figure 1 donne le chemin de donnée d'un processeur NON pipeliné (jeu d'instructions ARM). CP.

ARCHITECTURE DES ORDINATEURS Corrigé EXAMEN

ARCHITECTURE DES ORDINATEURS Corrigé EXAMEN

Soit le processeur DLX. Tous les registres ont 32 bits. Page 2. IFIPS-3. 2004-2005. 2. Le processeur a 32 registres entiers de R0 à R31. Le registre R0 est

Examen – Architecture des ordinateurs

Examen – Architecture des ordinateurs

processeur pipeliné à 4 étages possédant une structure de cache/bus permettant l'accès parallèle aux instructions et aux données (comme on l'a vu en cours).

Architecture des ordinateurs Corrigé de lexamen

Architecture des ordinateurs Corrigé de lexamen

Vos réponses aux questions de cours pourront comporter des exemples. 1.1 Pipeline. Expliquez en moins d'une page

Recueil dexercices corrigés en INFORMATIQUE I

Recueil dexercices corrigés en INFORMATIQUE I

d'un ordinateur sans passer par le processeur. Exercice 5. Processeur. - Gamme Lazard 'Architecture de l'ordinateur - Synthèse de cours et exercices corrigés ...

ARCHITECTURE DES ORDINATEURS

ARCHITECTURE DES ORDINATEURS

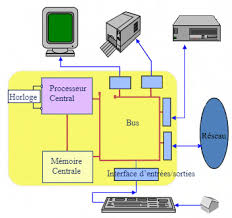

Evaluation : Contrôle continu : 40% Examen : 60%. Introduction. L'architecture Cours : Architecture des Ordinateurs. 15. 2.3. Processeur. Le processeur (CPU ...

ARCHITECTURE DES ORDINATEURS Corrigé Examen Décembre

ARCHITECTURE DES ORDINATEURS Corrigé Examen Décembre

Licence d'Informatique (L313). 3/8. On suppose que le processeur utilisé a un cache données de 64 Ko avec des lignes de 64 octets. Le cache utilise la

ARCHITECTURE DES ORDINATEURS Corrigé Examen Décembre

ARCHITECTURE DES ORDINATEURS Corrigé Examen Décembre

Le processeur a des registres de 32 bits et des adresses de 32 bits. Le cache est à réécriture (write back) et allocation d'écriture (il y a des défauts de

ARCHITECTURE DES ORDINATEURS Correction Examen Janvier

ARCHITECTURE DES ORDINATEURS Correction Examen Janvier

PARTIE 3 : CACHES. On considère que le processeur décrit en annexe a un cache donnée de 8 Ko avec des blocs. (lignes) de 16 octets.

Recueil dexercices corrigés en INFORMATIQUE I

Recueil dexercices corrigés en INFORMATIQUE I

vues pendant ses cours de l'Architecture de l'Ordinateur. Logiciels de Bureautique et Quels sont liens physiques entre le processeur et la mémoire ?

ARCHITECTURE DES ORDINATEURS Correction Examen Janvier

ARCHITECTURE DES ORDINATEURS Correction Examen Janvier

PARTIE 3 : CACHES. On considère que le processeur décrit en annexe a un cache donnée de 8 Ko avec des blocs. (lignes) de 16 octets.

Examen – Architecture des ordinateurs

Examen – Architecture des ordinateurs

13 févr. 2022 3- Un processeur à 1000 MHz a été utilisé pour exécuter un programme de ... Corrigé Examen –Architecture des ordinateurs (du 13 /02 / 2022).

Examen – Architecture des ordinateurs

Examen – Architecture des ordinateurs

30 mars 2021 Exercice 1 TD : (Test TD sur 6 points). I/ Soit un ordinateur à architecture bus système composé d'un processeur travaillant à une fréquence ...

Examen final – INF2500 Architecture des ordinateurs Automne

Examen final – INF2500 Architecture des ordinateurs Automne

Examen final – INF2500 Architecture des ordinateurs horloge du processeur sur le RAS et 6 périodes horloge du processeur sur le CAS. L'ordinateur sera.

ARCHITECTURE DES ORDINATEURS Corrigé Examen Décembre

ARCHITECTURE DES ORDINATEURS Corrigé Examen Décembre

MICROARCHITECTURES ET TEMPS D'EXECUTION DE PROGRAMMES. La figure 1 donne le chemin de donnée d'un processeur NON pipeliné (jeu d'instructions ARM). CP.

ARCHITECTURE DES ORDINATEURS Examen Décembre 2005

ARCHITECTURE DES ORDINATEURS Examen Décembre 2005

ARCHITECTURE DES ORDINATEURS. Examen Décembre 2005 (CORRIGÉ) Soient les processeurs non pipelinés (figure 1) et pipelinés (figure 2).

Examen – Architecture des ordinateurs

Examen – Architecture des ordinateurs

Examen – Architecture des ordinateurs Questions de cours (55 pts) ... Les instructions exécutées sur un processeur peuvent être classées en trois ...

Examen – Architecture des ordinateurs

Examen – Architecture des ordinateurs

Expliquer en quelques lignes le principe de pipelining. 2. On suppose que l'on dispose d'un processeur pipeliné à 5 étages dont le temps de cycle est de. 0.4ns

ARCHITECTURE DES ORDINATEURS Examen Décembre 2006

ARCHITECTURE DES ORDINATEURS Examen Décembre 2006

MICROARCHITECTURES ET TEMPS D'EXECUTION DE PROGRAMMES. La figure 1 donne le chemin de donnée d'un processeur NON pipeliné (jeu d'instructions ARM). CP.

Cours: architecture des ordinateurs

Cours: architecture des ordinateurs

Examen final – INF2500 Architecture des ordinateurs Automne 2001 – Toute documentation et la calculatrice sont permises Écrire vos résultats de façon claire et précise Pour les questions à développement montrer les calculs les réponses seules ne sont pas suffisantes Question 1 – (3 points)

Examen – Architecture des ordinateurs - University of Paris

Examen – Architecture des ordinateurs - University of Paris

Examen – Architecture des ordinateurs Mardi 15 mai 2012 - durée 2h Les documents de cours et de TD/TP sont interdits Seule est autorisée une feuille A4 de notes personelles approuvée par les suveillants du partiel Cette feuille devra être rendue avec la copie Les ordinateurs calculatrices ainsi que les téléphones sont interdits

Examen Final L2 (Architecture des ordinateurs) Durée 1h00 Le

Examen Final L2 (Architecture des ordinateurs) Durée 1h00 Le

Examen Final L2 (Architecture des ordinateurs) Durée 1h00 Le 22/01/2021 Bon courage Corrigé de l’examen Architecture des ordinateurs Exercice 1 (6 points) Soit K bits la taille du registre d’adresses (RA) et N bits la taille d’un mot mémoire 1 Exprimer la capacité de la mémoire centrale en octets et en mots

ARCHITECTURE DES ORDINATEURS Corrigé Examen Décembre 2011 3H

ARCHITECTURE DES ORDINATEURS Corrigé Examen Décembre 2011 3H

ARCHITECTURE DES ORDINATEURS Corrigé Examen Décembre 2011 3H – Tous documents autorisés Les questions sont indépendantes On utilise le jeu d’instructions ARM PROGRAMMATION ASSEMBLEUR PREMIERE PARTIE Soit le code C int a b; short c; unsigned char d; // Les adresses de a b c d sont initialement // dans R1 R2 R3 R4 a= (int) c;

Quels sont les cours d’architecture des ordinateurs?

Architecture des Ordinateurs Cours : Architecture des ordinateurs Support destiné aux étudiants de L1, L2 en Informatique. Dr. Soraya TIGHIDET Enseignante au Département d’Informatique Faculté des Sciences Exactes Université Abderrahmane Mira de Bejaia Avant-propos

Comment fonctionnent les processeurs sur les ordinateurs modernes ?

Voici quelques explications de fonctionnement des processeurs sur les ordinateurs modernes. Les processeurs fonctionnement à une certaine cadence et fréquences de l’horloge (en GHz). La technologie a atteint ses limites en terme de vitesse à cause des surchauffes provoquées lors des calcules.

Quelle est l’architecture d’un processeur ?

Enfin à ne pas confondre avec les architectures : amd64: pour les PC avec des processeurs Intel et AMD 64-bits i386: à destination des PC avec des processeur Intel et AMD 32-bits Pour comprendre l’architecture du processeur, lire : x64, x32, AMD64, i386, ARM64, i686 : les différences Télécharger les ISO Debian (Linux)

Qu'est-ce que l'architecture externe d'un processeur ?

Leur nombre dépasse les quelques Mo 2 à 3 sur la dernière génération de processeur en cache de niveau 2 et 3 Une architecture externe de processeur définit un ensemble de registres, dits architecturaux, qui sont accessibles par son jeu d'instructions. Ils constituent l'état externe (architectural) du processeur.