Recueil dexercices corrigés en INFORMATIQUE I

Recueil dexercices corrigés en INFORMATIQUE I

Recueil d'exercices corrigés en INFORMATIQUE I. (Architecture de l'ordinateur logiciels de bureautique et Internet et technologie web). L. Ghalouci

Architecture des ordinateurs Corrigé du TD 1 : Arithmétique des

Architecture des ordinateurs Corrigé du TD 1 : Arithmétique des

Architecture des ordinateurs. Corrigé du TD 1 : Arithmétique des ordinateurs et codage. Arnaud Giersch Benoît Meister et Frédéric Vivien.

Architecture des ordinateurs Corrigé du TD 2 : Arithmétique des

Architecture des ordinateurs Corrigé du TD 2 : Arithmétique des

Indiquer la valeur codée par la suite 1101100101110101 qui représente un entier signé en complément à 2 sur 16 bits. Correction : C'est un nombre négatif.

Architecture des ordinateurs Corrigé du TD 3 : Algèbre de Boole

Architecture des ordinateurs Corrigé du TD 3 : Algèbre de Boole

Architecture des ordinateurs. Corrigé du TD 3 : Algèbre de Boole. Arnaud Giersch Benoît Meister et Frédéric Vivien. 1. Montrer comment l'opérateur et peut

Architecture des ordinateurs Corrigé du TD 3 : Algèbre de Boole

Architecture des ordinateurs Corrigé du TD 3 : Algèbre de Boole

Architecture des ordinateurs. Corrigé du TD 3 : Algèbre de Boole. Arnaud Giersch Benoît Meister et Frédéric Vivien. 1. Montrer comment l'opérateur et peut

Architecture des ordinateurs Corrigé du TD 4 : Circuits combinatoires

Architecture des ordinateurs Corrigé du TD 4 : Circuits combinatoires

Architecture des ordinateurs. Corrigé du TD 4 : Circuits combinatoires. Arnaud Giersch Benoît Meister et Frédéric Vivien. 1. Exprimer la fonction xor comme

Architecture des ordinateurs Corrigé du TD 7 : Circuits séquentiels

Architecture des ordinateurs Corrigé du TD 7 : Circuits séquentiels

Architecture des ordinateurs. Corrigé du TD 7 : Circuits séquentiels (suite) La valeur d'entrée avant et après le mot est de 0. Correction : t d1.

ELECTRONIQUE NUMERIQUE + ARCHITECTURE DES

ELECTRONIQUE NUMERIQUE + ARCHITECTURE DES

Guy Almouzni. ELECTRONIQUE NUMERIQUE. +. ARCHITECTURE DES ORDINATEURS. CORRIGES TD 1 Corrigé. Logique combinatoire 1 ... TD 1 ANNEXE CORRIGE.

Architecture des Ordinateurs corrigé TD 1 Fonctions booléennes

Architecture des Ordinateurs corrigé TD 1 Fonctions booléennes

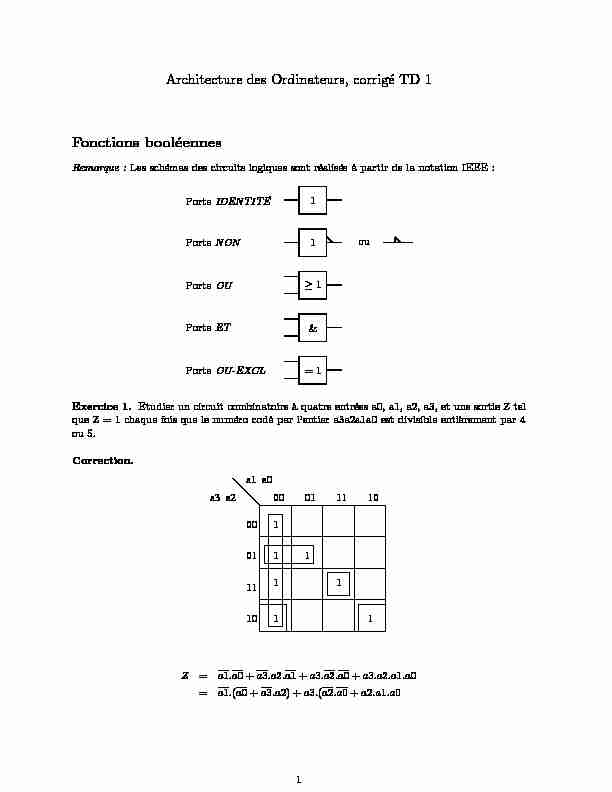

Architecture des Ordinateurs corrigé TD 1. Fonctions booléennes. Remarque : Les schémas des circuits logiques sont réalisés `a partir de la notation IEEE :.

ARCHITECTURE DES ORDINATEURS Corrigé Examen Décembre

ARCHITECTURE DES ORDINATEURS Corrigé Examen Décembre

ARCHITECTURE DES ORDINATEURS. Corrigé Examen Décembre 2011. 3H – Tous documents autorisés. Les questions sont indépendantes.

Exercices et Examens Architecture des ordinateurs PDF Corrigé

Exercices et Examens Architecture des ordinateurs PDF Corrigé

donnez le chronogramme des sorties Q de chacune des bascules câblées ci- dessous en fonction d’une entrée d’horloge H Exercice 2 1 Donnez la table de vérité du montage ci-dessous : 2 Quelle fonction reconnaissez-vous ? Exercice 3 On dispose de bascules JK synchronisées sur front montant Chaque bascule possède des entrées

Architecture des ordinateurs Corrigé du TD 1 : Arithmétique

Architecture des ordinateurs Corrigé du TD 1 : Arithmétique

Architecture des ordinateurs Corrigé du TD 1 : Arithmétique des ordinateurs et codage Arnaud Giersch Benoît Meister et Frédéric Vivien 1 Donner la valeur décimale des entiers suivants la base dans laquelle ces entiers sont codés étant précisée (a) 1011011 et 101010 en binaire (base 2); Correction : 10110112 = 9110 1010102 = 4210

Architecture des ordinateurs Corrigé du TD 6 : Circuits

Architecture des ordinateurs Corrigé du TD 6 : Circuits

Architecture des ordinateurs Corrigé du TD 6 : Circuits séquentiels Architecture des ordinateurs Corrigé du TD 6 : Circuits séquentiels Arnaud Giersch Benoît Meister et Frédéric Vivien 1 Bascules T On considère une bascule dont la table de vérité est la suivante On considère que ?est petit par rapport à un cycle d’horloge

Comment télécharger le cours d’architecture des ordinateurs ?

Tout en PDF/PPT, Tout est gratuit. NOTE: N’oubliez pas de voir le cours de Architecture des ordinateurs. Liens dans la section ci-dessous. Pour télécharger le cours complet d’Architecture des ordinateurs, Cliquez sur le/les liens ci-dessous. NOTE: N’oubliez pas de voir les autres Unités d’enseignements (matières/modules) d’Informatique.

Comment voir les modules de la filière informatique ?

Liens dans la section ci-dessous. Tourner à la page principale d’Informatique pour voir la totalité des modules (cours, résumés, formation, exercices, td, examens, qcm, livres). Ou visiter directement les exercices des autres modules de la filière informatique à partir de ces liens ci-dessous:

Comment voir les autres unités d’enseignements d’informatique ?

NOTE: N’oubliez pas de voir les autres Unités d’enseignements (matières/modules) d’Informatique. Liens dans la section ci-dessous. Tourner à la page principale d’Informatique pour voir la totalité des modules (cours, résumés, formation, exercices, td, examens, qcm, livres).

Architecture des Ordinateurs, corrig´e TD 1

Fonctions bool´eennes

Remarque :Les sch´emas des circuits logiques sont r´ealis´es `a partir de la notation IEEE :

PorteIDENTIT´E

1PorteNON1ou

PorteOU≥1

PorteET&

PorteOU-EXCL= 1

Exercice 1.Etudier un circuit combinatoire `a quatre entr´ees a0, a1, a2, a3, et une sortie Z telque Z = 1 chaque fois que le num´ero cod´e par l"entier a3a2a1a0 est divisible enti`erement par 4

ou 5.Correction.

00 01 11 10

00 01 1110a3 a2

a1 a0 1 111 11 11

Z=a1.a0 +a3.a2.a1 +a3.a2.a0 +a3.a2.a1.a0

a1.(a0 +a3.a2) +a3.(a2.a0 +a2.a1.a0 1 d"o`u le sch´ema : 1 1& 1 a3 a2 a1 a0 ZExercice 2.On consid`ere un ascenceur desservant un rez-de chauss´ee et trois ´etages. L"unit´e

logique de contrˆole de cet ascenceur re¸coit en entr´ee desrequˆetes de d´eplacement d"un ´etage vers

un autre, et g´en`ere en sortie les commandes correspondantes destin´ees au moteur de la cage. Il

s"agit de r´ealiser les circuits qui composent l"unit´e de contrˆole. Pour cela :- La valeur de l"´etage d"o`u part la requˆete (de 0 `a 3) est cod´ee par deux variables bool´eennes

x1 etx2. La valeur courante de l"´etage o`u se trouve la cage de l"ascenceur est cod´ee de fa¸con similaire par deux variables bool´eennesx3 etx4.- La sortie de l"unit´e de contrˆole est constitu´ee de troisfonctions bool´eennesHaut, Bas,

Stopdes quatre variables d"entr´eex1,x2,x3, etx4.Haut(x1,x2,x3,x4) est vraie quand la position courante de la cage estau-dessousde l"´etage d"o`u part la requˆete et fausse autrement. Inversement,Bas(x1,x2,x3,x4) est vraie quand la position courante de la cage estau-dessusde l"´etage d"o`u part la requˆete et fausse autrement. Finalement, Stop(x1,x2,x3,x4) est vraie quand l"´etage d"o`u part la requˆete et la position courante de l"ascenceur sont lesmˆemes,et fausse autrement.On vous demande de :

1. repr´esenter chacune des fonctions de l"unit´e de contrˆole par une table de Karnaugh;

2. simplifier ces fonctions;

3. dessiner les sch´emas des circuits correspondant `a chacune des fonctions simplifi´ees, en

utilisantle plus petit nombre possiblede portes.Correction.La valeur de l"´etage d"o`u part la requˆete est repr´esent´ee par la table binaire sui-

vante : x1x2Etage00Rez-de-chauss´ee

011er 102d113`eme

2De mˆeme, la valeur courante de l"´etage o`u se trouve la cagede l"ascenceur est repr´esent´e par la

table binaire : x3x4Etage00Rez-de-chauss´ee

011er 102d113`eme

Pour la fonction bool´eenneHaut(x1,x2,x3,x4)par exemple, il suffit de remplir une table deKarnaugh `a quatre variables de telle fa¸con que pour chaquecase un "1" y est plac´e si la valeur

courante de l"´etage o`u se trouve la cage de l"ascenceur estplus basse que la valeur de l"´etage d"o`u

part la requˆete, et un "0" y est plac´e sinon :00 01 11 10

00 01 11 10 x1 x2x3 x4 1 1 11110 0 0 0

000 0 0 0 L"expression bool´eenne r´esultante apr`es simplificationest :Haut(x1,x2,x3,x4) =x1.

x3 +x2.x3.x4 +x1.x2.x4 Bien que cette expression soit une forme normale disjonctive minimale, il est possible de pousser la simplification plus loin : x1. x3 +x2.x3.x4 +x1.x2.x4 =x1.x3 +x2.x4.(x3 +x1) Le circuit obtenu a exactement sept portes logiques : 1111 x1 x2 x3 x4&

Haut (x1, x2, x3, x4)

3 Les autres fonctions bool´eennes sont ´etablies de la mˆememani`ere.Exercice 3.On d´esire r´ealiser le syst`eme inclus dans une calculettequi `a un digit d´ecimal fait

correspondre l"allumage de segments repr´esentant ce digit. Le digit ´etant cod´e sur quatre valeurs

A,B,C,D,calculer les sept fonctionsa,b,c,d,e,f,gcommandant l"´eclairement des segments correspondants : gf e dcbaCorrection.ABCDabcdefg

00001111110

00010110000

00101101101

00111111001

01000110011

01011011011

01101011111

01111110000

10001111111

10011111011

1010xxxxxxx

1011xxxxxxx

1100xxxxxxx

1101xxxxxxx

1110xxxxxxx

1111xxxxxxx

1101 1 1

1 110X X X X00 01 11 10

00 01 1110A B

C D X X 4 a=A+C+B.D+B.D g=A+B.C+B.C+C.D

Exercice 4.R´ealisation d"un additionneur/soustracteur (portes logiques disponibles :ET,OU,NON,OU EXCL)

1. R´ealiser un demi-soustracteur (1 bitAavec 1 bitBsans retenue d"entr´ee) :

- Ecrire la table de v´erit´e. - Donner les ´equations de sortie. - Etablir le sch´ema logique.2. En comparant le circuit du demi-soustracteur avec celui d"un demi-additionneur, conce-

voir le plus simplement possible un circuit, appel´e demi-additionneur/soustracteur, qui `a partir d"un signal de commandeCet des entr´eesAetB, simule le demi-additionneur surAetBlorsque la commandeCest `a 0, et le demi-soustracteur surAetBlorsque la commandeCest `a 1 (suggestion : appliquer le signal de commande `a une des entr´ees d"une porteOU EXCL).3. A partir du demi-additionneur/soustracteur qui vient d"ˆetre r´ealis´e, concevoir un addi-

tionneur/soustracteur complet (1 bitAavec un bitBavec retenue d"entr´ee).4. Donner le sch´ema d"un additionneur/soustracteur quatre bits par quatre bits.

Correction.

1. Undemi-soustracteurest un circuit qui soustrait simplement un bit d"un autre. Ler´esultat

est obtenu sur deux bits,Spour le poids faible (la diff´erence),Rpour le poids fort (la retenue). A partir de la table de v´erit´e suivante : ABRS 0000 01111001

1100

on obtient : S=

A.B+A.B

=A?B R= A.B 5 Le demi-soustracteur est r´ealis´e par le circuit suivant : A B= 1S &R2. On constate que la seule diff´erence entre un demi-soustracteur et un demi-additionneur

tient `a la pr´esence d"une n´egation sur l"entr´eeAde la porte ET qui g´en`ere la rete- nue. L"ajout d"une porte OU EXCL dont une des entr´ees est la commandeCdoit donc permettre de simuler la n´egation pr´esente dans le demi-soustracteur lorsqueC= 1, etl"absence de cette n´egation dans le demi-additionneur lorsqueC= 0. Il est ais´e de v´erifier

partir de la table de v´erit´e de OU EXCL qu"il suffit de prendre directementApour l"autre entr´ee de la porte OU EXCL : lorsqueC= 0, la sortie de la porte est ´equivalente `aA, lorsqueC= 1cette sortie prend la valeur de A.C AC?A

0 00 0 11 1 01 1 10Bien entendu, une ´etude syst´ematique des sorties `a partir de toutes les entr´ees permet de

retrouver les ´equations bool´eennes attendues :C A BRS

0 0 000

0 0 101

0 1 001

0 1 110

1 0 000

1 0 111

1 1 001

1 1 100

on obtient : S=C.A.B+C.A.B+C.A.B+C.A.B

C.(A?B) +C.(A?B)

C+C).(A?B)

=A?B R=C.A.B+C.A.B

C.A+C.A).B

= (C?A).B 6 Le sch´ema d"un demi-additionneur/soustracteur est donc : A B= 1S &R = 1C3. La table de v´erit´e de l"additionneur/soustracteur est(avecRe, retenue en entr´ee etRs

retenue en sortie) :C ReA BRsS

0 0 0 000

0 0 0 101

0 0 1 001

0 0 1 110

0 1 0 001

0 1 0 110

0 1 1 010

0 1 1 111

1 0 0 000

1 0 0 111

1 0 1 001

1 0 1 100

1 1 0 011

1 1 0 110

1 1 1 000

1 1 1 111

on obtient : S=C.Re.A.B+C.Re.A.B+C.Re.A.B+C.Re.A.B+

C.Re.A.B+C.Re.A.B+C.Re.A.B+C.Re.A.B

C+C).Re.A.B+ (C+C).Re.A.B+ (C+C).Re.A.B+ (C+C).Re.A.BRe.(A.B+A.B) +Re.(A.B+A.B)

Re.(A?B) +Re.A?B

=Re?A?B R=C.Re.A.B+C.Re.A.B+C.Re.A.B+C.Re.A.B+

C.Re.A.B+C.Re.A.B+C.Re.A.B+C.Re.A.B

C.Re.(A.B+A.B) +C.Re.(A.B+A.B) +C.(Re+Re).A.B+C.(Re+Re).A.BC.(A?B) +C.(A?B)).Re+ (C.A+C.A).B

= (C?A?B).Re? R2+(C?A).B????

R 1 7 Le sch´ema de l"additionneur/soustracteur est imm´ediat : C A B Re1/2-a-s1/2-a-s

≥1 S R2R1 Rs4. Le sch´ema d"un additionneur/soustracteur quatre bits par quatre bits s"obtient de fa¸con

toute aussi imm´ediate :Add/SouAdd/SouAdd/SouAdd/Sou0

S3S2S1S0R

2R1R0D´epassementB

3B2B1B0A3A2A1A0

C 8Exos suppl´ementairesExercice 5.

1. Exprimer les op´erateursNON,ET,OUen fonction de l"unique op´erateurNON-OU,

r´esultant de la composition deNONetOU, et vu comme un op´erateur bool´een `a part enti`ere d´efini par :NON-OU(x,y) =

x+y2. Exprimer avec desNON-OUuniquement l"expression bool´eenne suivante :

((x1+x2).(x3+x4.x5)). x63. Dessiner ensuite le sch´ema logique correspondant.

Correction.

NON x=x+xETx.y=

x.y=x+y=x+x+y+yOUx+y=

x+y=x+y+x+y f(x1,x2,x3,x4,x5,x6) = ((x1+x2).(x3+x4.x5))? x 7.x6 x7+x7+x6 x7+x7+x6 x7= (x1+x2).(x3+x4.x5))

(x1+x2) + (x1+x2) +(x3+x4.x5) + (x3+x4.x5) (x1+x2) +(x3+x4.x5) x 4.x5= x4+x4+x5+x5 d"o`u : x 7= x1+x2+x3+x4+x4+x5+x5 1 1111 11 1x4 x 6x 5x 3x7x 1x2 9 Exercice 6.R´ealisation d"un multiplicateur 2 bits par 2 bits : - R´ealiser un circuit qui effectue la multiplication 1 bit par1 bit. - R´ealiser un multiplicateur 2 bits par 2 bits - directement `a l"aide de portesET,OU,NON,NON-ET,NON-OU... - alternativement, `a l"aide du multiplicateur 1 bit par 1 bit r´ealis´e ci-dessus et de demi- additionneurs.

Correction.

1. Circuit qui effectue la multiplication 1 bit par 1 bit :aetb´etant les deux bits `a multiplier,

la fonction bool´eenneP=a.b2. On notea1a0les deux bits du premier nombre, etb1b0les deux bits du deuxi`eme nombre;

le r´esultat s"´ecrit sur 4 bitsp3p2p1p0. (a) b1b0a1a0p3p2p1p00 0 0 00 0 0 0

0 0 0 10 0 0 0

0 0 1 00 0 0 0

0 0 1 10 0 0 0

0 1 0 00 0 0 0

0 1 0 10 0 0 1

0 1 1 00 0 1 0

0 1 1 10 0 1 1

1 0 0 00 0 0 0

1 0 0 10 0 1 0

1 0 1 00 1 0 0

1 0 1 10 1 1 0

1 1 0 00 0 0 0

1 1 0 10 0 1 1

1 1 1 00 1 1 0

1 1 1 11 0 0 1

p3 =b1.b0.a1.a0 p2 =b1. b0.a1.a0 +b1.b0.a1.a0 +b1.b0.a1.a0 =b1. b0.a1.a0 +b1.b0.a1.a0 +b1.b0.a1.a0 +b1.b0.a1.a0 =b1. b0.a1 +b1.a1.a0 =b1.a1.( b0 +a0) =b1.a1. b0.a0 p1 = b1.b0.a1.a0 +b1.b0.a1.a0 +b1.b0.a1.a0 +b1.b0.a1.a0 +b1.b0.a1.a0 +b1.b0.a1.a0 b1.b0.a1 +b1.b0.a0 +b1.b0.(a1?a0) b1.b0.a1 +b1.(b0.a0 +b0.(a1?a0)) p0 = b1.b0.a1.a0 +b1.b0.a1.a0 +b1.b0.a1.a0 +b1.b0.a1.a0 b1.b0.a0 +b1.b0.a0 =b0.a0 10 (b) Remarquons que (d´eveloppement polynˆomial d"un nombre en base 2) : a1a0 =a1×21+a0×20 b1b0 =b1×21+b0×20 Rappelons que l"exposant associ´e `a la base correspond au rang de chacun des bits qui codent le nombre. On a alors : a1a0×b1b0 = (a1×21+a0×20)×(b1×21+b0×20) =a1×b1×22+ (a1×b0 +a0×b1)×21+a0×b0×20Dans cette ´equation

p0 =a0×b0 p1 =a1×b0 +a0×b1qui repr´esente une somme de deux bits r´ealis´ee avec un demi-additionneur, et donc g´en`ere une retenueR1de rang sup´erieur d"o`u : p2 =a1×b1 +R1qui repr´esente une somme de deux bits r´ealis´ee avec un demi-additionneur, et donc g´en`ere une retenueR2de rang sup´erieur d"o`u : p3 =R2Autrement dit,

p3p2p1p0 =R2×23+ (a1×b1 +R1)×22+ (a1×b0 +a0×b1)×21+ (a0×b0)×20Exemple :

11 a1a0 = 11

x 11 b1b0 = 11 11 111001 p3 = 1, p2 = 0, p1 = 0, p0 = 1

A partir des ´equation dep3,p2,p1,p0obtenues ci-dessus, on obtient le sch´ema :Mult 1-1Mult 1-1Mult 1-1

Add 1-1

Add 1-1

Mult 1-1

a1 a1b1 b1b0 b0a0 a0 p3 p2 p1 p0 11quotesdbs_dbs28.pdfusesText_34[PDF] signification des volumes

[PDF] genese de la forme architecturale

[PDF] la perception en architecture

[PDF] principe de composition architecturale

[PDF] architecture classique pdf

[PDF] architecture du 17ème siècle

[PDF] architecture classique 17ème siècle

[PDF] cours histoire de l'architecture renaissance

[PDF] architecture baroque exemple

[PDF] architecture 18e siècle france

[PDF] architecture classique et baroque

[PDF] architecture romaine antique pdf

[PDF] méthode de construction des romains

[PDF] architecture antique grecque