8086 Instruction Encoding-1 Encoding of 8086 Instructions ! 8086

8086 Instruction Encoding-1 Encoding of 8086 Instructions ! 8086

8086 Instruction Encoding-12. Examples (Cont'd) ! MOV instruction has seven possible formats. We will not discuss them all. MOV reg/memreg/mem ! This

80x86 Instruction Encoding 8086 Instructions Encoding of 8086

80x86 Instruction Encoding 8086 Instructions Encoding of 8086

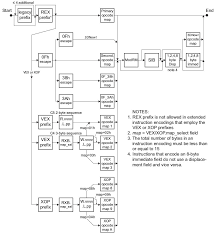

Encoding of 8086 Instructions. • 8086 instructions are encoded as binary numbers. • Instructions vary in length from 1 to 6 bytes. Note that many RISC

Instruction Encoding

Instruction Encoding

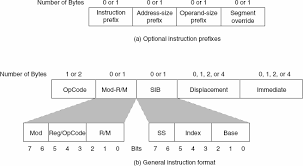

• Additional notes in : Instruction Encoding Note. SYSC3006. 1. Page 2. Instruction Encoding. On the Intel 8086 an instruction is a sequence of 1..6 bytes. • A

4- MACHINE LANGUAGE CODING 4-1THE INSTRUCTION SET

4- MACHINE LANGUAGE CODING 4-1THE INSTRUCTION SET

17 janv. 2018 The machine code instructions of the 8086 vary in the number of bytes used to encode them. Some instructions can be encoded with just 1 byte ...

ASM86 LANGUAGE REFERENCE MANUAL

ASM86 LANGUAGE REFERENCE MANUAL

Encoding. 9809 FO. Operation op1. Emulator. Encoding. CO 19 FO op2. Execution ... 8086/8088 flags. (see Flags). 8087 Control word 6-110. 8087 Data types

x86 Instruction Encoding

x86 Instruction Encoding

version of 8086 :-) – Page 4. 11 x86 ISA. ○ Insn set backwards-compatible to Intel 8086. • A hybrid CISC. • Little endian byte order. • Variable length ...

adaptTo() 2020

adaptTo() 2020

30 sept. 2020 CVE-2019-8086 / XML eXternal Entity Injection. ▫ CVE-2019-8087 / XML ... encoding="utf-8"?><!DOCTYPE afData [<!ENTITY a SYSTEM "file:///etc ...

Instructions Involve a Segment Register (SR-field) Encoding a

Instructions Involve a Segment Register (SR-field) Encoding a

The first byte of the program is stored at the lowest address. Page 2. 8086/8088MP. INSTRUCTOR: ABDULMUTTALIB A. H. ALDOURI. ٥٨.

Multiple Choice Questions on 8086 Microprocessor

Multiple Choice Questions on 8086 Microprocessor

data encoding. ANSWER: C. 78. In 8086 Example for Non maskable interrupts are . A. TRAP. B. RST6.5. C. INTR. D. RST6.6. ANSWER: A. 79. In 8086 the overflow

x86-64 encoding / viruses

x86-64 encoding / viruses

8 févr. 2021 (dedicated opcodes) pop ax … 6. Page 7. 8086 instruction encoding: two-arg. 1-byte opcode sometimes ModRM byte: 2-bit “mod” and. 3-bit register ...

8086 Instruction Encoding-1 Encoding of 8086 Instructions ! 8086

8086 Instruction Encoding-1 Encoding of 8086 Instructions ! 8086

8086 Instruction Encoding-1. Encoding of 8086 Instructions ! 8086 Instructions are represented as binary numbers. Instructions require between 1 and 6 bytes.

80x86 Instruction Encoding 8086 Instructions Encoding of 8086

80x86 Instruction Encoding 8086 Instructions Encoding of 8086

through x86-64 are backwardly compatible with the 8086. • We will look at 8086 encoding in detail 8086 instructions are encoded as binary numbers.

Instructions Involve a Segment Register (SR-field) Encoding a

Instructions Involve a Segment Register (SR-field) Encoding a

8086/8088MP. INSTRUCTOR: ABDULMUTTALIB A. H. ALDOURI. ??. Ex: Encode the “block move” program and show how it would be stored in.

Instruction Encoding

Instruction Encoding

Instruction Encoding. On the Intel 8086 an instruction is a sequence of 1..6 bytes. • A simple (and incomplete) model of an instruction is as follows.

x86-64 encoding / viruses

x86-64 encoding / viruses

8 févr. 2021 8086 instruction encoding: two-arg. 1-byte opcode sometimes ModRM byte: 2-bit “mod” and. 3-bit register number (source or dest ...

4- MACHINE LANGUAGE CODING 4-1THE INSTRUCTION SET

4- MACHINE LANGUAGE CODING 4-1THE INSTRUCTION SET

17 janv. 2018 The machine code instructions of the 8086 vary in the number of bytes used to encode them. Some instructions can be encoded with just 1 byte ...

x86 Instruction Encoding

x86 Instruction Encoding

8086: 1978 16-bit CPU with 16-bit external data bus Insn set backwards-compatible to Intel 8086 ... Encoding escapes: different encoding syntax.

8086 Programming

8086 Programming

23 oct. 2012 Instruction Encoding. How to encode instructions as binary values? Instructions consist of: • operation (opcode) e.g. MOV.

Instruction format

Instruction format

The machine code instructions of the 8086 vary in the number of bytes used to encode them. Some instructions can be encoded with just 1 byte others can be done

adaptTo() 2020

adaptTo() 2020

30 sept. 2020 CVE-2019-8086. 16. ? Exploitation hints. ? We can JSON-encode XXE payload to bypass a WAF*. ? In Java we can list directory content.

8086 Programming

Compiled by: Chandra Thapa

October 23, 2012

UNIT I

Concept (not important for exam and not in syllabus)Instruction Encoding

How to encode instructions as binary values?

Instructions consist of:

i operation (opcode) e.g. MOV i operands (number depends on operation) i operands specified using addressing modes i addressing mode may include addressing information i e.g. registers, constant values Encoding of instruction must include opcode, operands & addressing information.Encoding:

i represent entire instruction as a binary value i number of bytes needed depends on how much information must be encoded i instructions are encoded by assembler: i .OBJ file ! (link, then loaded by loader) i instructions are decoded by processor during execution cycleWe will consider a subset of interesting cases

Instructions with No Operands

(easy) i encode operation only in a single byte i examples: RETC3 H NOP 90 H

i Are consistent - never changeInstructions with One Operand

i operand is a register (reg8/16) or a memory operand (mem8/16) i always 2 bytes for opcode and addressing info i may have up to 2 more bytes of immediate data i opcode bits: some in both bytes! 10 bits total i w = width of operand0 = 8-bit

1 = 16-bit

i mod & r/m encode addressing info opcode w7 1 0

mod opcode r/m7 6 5 4 3 2 1 0

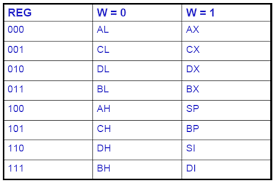

MOD / R/M TABLE

mod00 01 10 11

r/m w = 0 w = 1000 [BX + SI] [BX + SI + d] [BX + SI + n] AL AX

001 [BX + DI] [BX + DI + d] [BX + DI + n] CL CX

010 [BP + SI] [BP + SI + d] [BP + SI + n] DL DX

011 [BP + DI] [BP + DI + d] [BP + DI + n] BL BX

100 [SI] [SI + d] [SI + n] AH SP

101 [DI] [DI + d] [DI + n] CH BP

110 direct ad [BP + d] [BP + n] DH SI

111 [BX] [BX + d] [BX + n] BH DI

d is 8-bit signed value n is 16-bit unsigned value register direct address mod = 01 is not used by the assembler!Example:

INC DH

opcode : 1st byte: 1111111 2nd byte: 000 w = 0 (8-bit operand) operand = DH register: mod = 11 r/m = 110 opcode w1st byte: 1111111 0 = FE H

mod opcode r/m2nd byte: 11 000 110 = C6 H

What does following encoding represent?

11111111 11000111 = FF C7 H

opcode = INC 1st byte: 1111111 2nd byte: 000 w = 1 16-bit operand mod = 11 register operand r/m = 111 DI register encoding forINC DI !!!

Another Example:

INC BYTE PTR [SI - 4]

i indexed addressing to an 8-bit memory operand i will need extra byte(s) to encode the immediate value (4 = FFFC H) from table! opcode - same as last example: 111111 000 w = 0 8-bit destination (memory) operand r/m = 100 (from table) mod could be 01 or 10 depends on constant can use whichever mod value works can shorten encodings! the assembler will use mod = 1016-bit constant (FFFCH) encoded into instruction

little endian resulting instruction encoding: byte 1 byte 2 byte 3 byte 41111111 0 10 000 100 11111100 11111111

FE 84 FC FF H

Could also encode same instruction:

mod = 01 constant encoded as signed 8-bit value therefore instruction encoding includes only one byte for the encoding of - 4 resulting instruction encoding: byte 1 byte 2 byte 31111111 0 01 000 100 11111100

FE 44 FC

H N.B. the 8-bit value (- 4 = FC H) is sign extended to 16-bits (FFFC H) before adding SI value why?Another Example:

INC BYTE PTR [SI + 128]

i indexed addressing to an 8-bit memory operand i everything the same as last example, except: can "t encode +128 as 8-bit signed value! need 16-bits to encode 128 then must have mod = 10 !! instruction encoding would include two extra bytes encoding 128 = 00 80 H resulting instruction encoding: byte 1 byte 2 byte 3 byte 41111111 0 10 000 100

FE 84 00 80 H

Instructions with Two Operands (2 Forms)

i at most, can have only one memory operand i can have 0 or 1 memory operands, but not 2 i limits max. instruction size to 6 bytes little endian mod ! value of most signif. bit of byte is copied to all bits in extension byte i e.g. MOV WORD PTR [BX+ 500], 0F0F0H i 2 bytes opcode + addressing info i 2 bytes destination addressing constant 500 i 2 bytes source constant F0F0 H FORM 1: Two Operands And Source Uses Immediate Mode i destination either register or memory i encode dest using mod & r/m - as before w (as before) = size of operand (8- or 16-bit) if w = 1 (16-bit) then s is significant s indicates size of immediate value0 all 16-bits encoded in instruction

assembler always used s = 0 = 1 8-bits encoded - sign extend to 16-bits!Example:

SUB My_Var, 31H

i My_Var is a word (DW) stored at address 0200H opcode bits: 1st byte: 100000 2nd byte: 101 w = 1 (16-bit memory operand) s = 1 - can encode 31H in one byte sign extend to 0031H opcode s w7 2 1 0

mod opcode r/m7 6 5 4 3 2 1 0

mod = 00 r/m = 110 resulting encoding: opcode100000 1 1 00 101 110 2-bytes dest 1-byte

address imm s w mod r/m83 2E 02 00 31

FORM 2: Two Operands And Source Does Not Use Immediate Mode i at least one of destination or source is register! i encode register operand i encode other using mod & r/m - as before d = destination0 source is encoded in REG

1 destination is encoded in REG

opcode d w7 2 1 0

mod REG r/m7 6 5 4 3 2 1 0

destination: direct addressing stored little endian assembler uses s = 0 & 16-bit immediate value31 00 (little endian)

Example: SUB My_Var , SI

opcode:0010 10

suppose My_Var is @ address 0020H d = 0 - source is a register - encoded in REG w = 1 - 16-bit operand mod = 00 destination is memory - direct mode r/m = 110REG = 110

(SI) encoding:001010 0 1 00 110 110 addrs const

29 36 20 00

NOTE : different first-byte opcode bits for SUB when source is immediate (100000) vs. when source is not immediate (001010) The opcode bits for FORM 1 vs. FORM 2 instructions are different!MOV [BX], 200

MOV [BX] , AX

i what if both source and destination are registers? i should REG encode source or destination?Example: SUB BX, CX

d w mod register encoding as in mod = 11 column in table different opcode bits! r/mCase 1: Source (CX) is encoded in REG

opcode: 0010 10 d = 0 - source is encoded in REG w = 1 - 16-bit operand mod = 11 destination is register r/m = 011 BX register is destination registerREG = 001

CX register is source register

encoding:001010 0 1 11 001 011

29 CB

Case 2:

Destination (BX) is encoded in REG

opcode: 0010 10 d = 1 - destination is encoded in REG w = 1 - 16-bit operand mod = 11 source is register r/m = 001 CX register (source)REG = 011

BX register (destination)

encoding:001010 0 1 11 011 001

29 D9

d w mod r/m i cases 1 & 2: two encodings for same instruction!Some Special-Case Encodings:

i single-operand instructions & operand is 16-bit register - can encode in one byte i instructions involving the accumulator:AL or AX

i shorter encoded forms - often one byteWHY? What use are these special cases?

Instruction Encoding (human perspective)

1. given instruction - how to encode ? 2. given binary - how to decode ?Given instruction - how to encode ?

i decide on form & number of bytes i find opcode bits from table i decide on remaining bits y individual bit values y look up mod & r/m values if needed y look up register encoding if needed i fill opcode byte(s) i add immediate operand data byte(s) y words little endian y dest precedes sourceGiven binary - how to decode ?

i use first 6 bits of first byte to decide on form & number of bytes i use opcode bits to find operation from table i identify operands from remaining bits y individual bitsWhy might this be important? EXAM !!!!

y look up mod & r/m values if present y look up register encoding if present i add immediate operand data byte(s) if presentquotesdbs_dbs12.pdfusesText_18[PDF] 8086 instruction format example

[PDF] 8086 instruction format pdf

[PDF] 8086 instruction set and assembler directives pdf

[PDF] 8086 instruction set opcodes pdf

[PDF] 8086 instruction set pdf

[PDF] 8086 instruction set pdf download

[PDF] 8086 instruction set pdf nptel

[PDF] 8086 instruction set slideshare

[PDF] 8086 kit lab manual

[PDF] 8086 microprocessor architecture and instruction set

[PDF] 8086 microprocessor architecture and pin diagram pdf

[PDF] 8086 microprocessor architecture and pin diagram ppt

[PDF] 8086 microprocessor architecture diagram

[PDF] 8086 microprocessor architecture explanation